M1AFS-ADV-DEV-KIT-PWR Actel, M1AFS-ADV-DEV-KIT-PWR Datasheet - Page 33

M1AFS-ADV-DEV-KIT-PWR

Manufacturer Part Number

M1AFS-ADV-DEV-KIT-PWR

Description

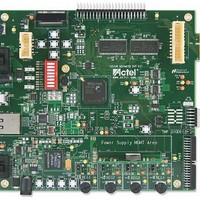

MCU, MPU & DSP Development Tools Fusion Advanced Dev Kit w/ Power

Manufacturer

Actel

Datasheet

1.M1AFS-ADV-DEV-KIT-PWR.pdf

(94 pages)

Specifications of M1AFS-ADV-DEV-KIT-PWR

Processor To Be Evaluated

M1AFS1500-FGG484

Interface Type

Ethernet, USB, I2C, UART

Operating Supply Voltage

1.5 V to 5 V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

RealView Header

Ethernet Interface

Fusion Advanced Development Kit User’s Guide

One 10×2 RealView Header is provided on the board for debugging

software development tools to easily debug or configure the embedded Cortex-M1 processor during board bring-up.

One Ethernet interface, configured for MII Full Duplex mode, and a low-power 10/100 Mbps single-port Ethernet

physical layer transceiver (U10) are provided on-board

integrated sub-layers to support both 10BASE-T and 100BASE-TX Ethernet protocols. These sub-layers ensure

compatibility and interoperability with many other standards-based Ethernet solutions.

Two LEDs are populated on the board for this ethernet interface. One is for speed and the other is for activity.

The Ethernet RJ45 interface and physical layer, along with an Ethernet Media Access Controller (MAC) that can be

programmed onto the M1-enabled Fusion FPGA, serves many purposes. For example, this interface can be used to

access the Fusion FPGA to monitor the ADC data over a network

control registers can be accessed and processed remotely to support system management. The Actel IP catalog includes a

Core10100 Ethernet MAC with Host Controller.

Microprocessor

M1 Embedded

Fusion FPGA

{5}

{5}

{5}

{5}

{5}

{5}

{5}

{5}

{5}

{5}

RVI-ME_VTref

RVI-ME_nTRST

RVI-ME_TDI

RVI-ME_TMS

RVI-ME_TCK

RVI-ME_RTCK

RVI-ME_TDO

RVI-ME_nSRST

RVI-ME_DBGRQ

RVI-ME_DBGACK

TO DUT

Figure 2-24 · RealView Header Schematic

Figure 2-25 · Typical Application

Physical Layer

Ethernet

Mfr P/N :HTST-110-01-L-DV

Mfr: SAMTEC

(Figure 2-26 on page

11

13

15

17

19

1

3

5

7

9

J5

J5

HEADER 10X2

HEADER 10X2

(Figure

1

3

5

7

9

11

13

15

17

19

(Figure

Components Descriptions and Connections

2-25). The embedded system memory and

34). The Ethernet physical layer features

2-24). This header allows RealView

10

12

14

16

18

20

2

4

6

8

2

4

6

8

10

12

14

16

18

20

10BASE-T or

100BASE-TX

33