AGL400V5-FGG484 Actel, AGL400V5-FGG484 Datasheet - Page 109

AGL400V5-FGG484

Manufacturer Part Number

AGL400V5-FGG484

Description

FPGA - Field Programmable Gate Array 400K System Gates

Manufacturer

Actel

Datasheet

1.AGL030V2-CSG81.pdf

(236 pages)

Specifications of AGL400V5-FGG484

Processor Series

AGL400

Core

IP Core

Number Of Logic Blocks

12

Maximum Operating Frequency

250 MHz

Number Of Programmable I/os

194

Data Ram Size

54 Kbit

Supply Voltage (max)

1.5 V

Supply Current

27 uA

Maximum Operating Temperature

+ 70 C

Minimum Operating Temperature

0 C

Development Tools By Supplier

AGL-Icicle-Kit, AGL-Dev-Kit-SCS, Silicon-Explorer II, Silicon-Sculptor 3, SI-EX-TCA, FlashPro 4, FlashPro 3, FlashPro Lite

Mounting Style

SMD/SMT

Supply Voltage (min)

1.425 V

Number Of Gates

400 K

Package / Case

FPBGA-484

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AGL400V5-FGG484

Manufacturer:

Actel

Quantity:

135

Company:

Part Number:

AGL400V5-FGG484

Manufacturer:

Microsemi SoC

Quantity:

10 000

Company:

Part Number:

AGL400V5-FGG484I

Manufacturer:

Microsemi SoC

Quantity:

10 000

- Current page: 109 of 236

- Download datasheet (8Mb)

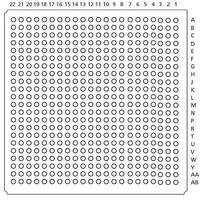

Figure 2-22 • Input DDR Timing Diagram

Table 2-163 • Input DDR Propagation Delays

Out_QR

Out_QF

Parameter

t

t

t

t

t

t

t

t

t

t

t

t

t

F

Note:

DDRICLKQ1

DDRICLKQ2

DDRISUD1

DDRISUD2

DDRIHD1

DDRIHD2

DDRICLR2Q1

DDRICLR2Q2

DDRIREMCLR

DDRIRECCLR

DDRIWCLR

DDRICKMPWH

DDRICKMPWL

DDRIMAX

Data

CLK

CLR

For specific junction temperature and voltage supply levels, refer to

Timing Characteristics

Commercial-Case Conditions: T

1.5 V DC Core Voltage

t

t

1

DDRICLR2Q1

DDRICLR2Q2

Clock-to-Out Out_QR for Input DDR

Clock-to-Out Out_QF for Input DDR

Data Setup for Input DDR (negedge)

Data Setup for Input DDR (posedge)

Data Hold for Input DDR (negedge)

Data Hold for Input DDR (posedge)

Asynchronous Clear-to-Out Out_QR for Input DDR

Asynchronous Clear-to-Out Out_QF for Input DDR

Asynchronous Clear Removal Time for Input DDR

Asynchronous Clear Recovery Time for Input DDR

Asynchronous Clear Minimum Pulse Width for Input DDR

Clock Minimum Pulse Width High for Input DDR

Clock Minimum Pulse Width Low for Input DDR

Maximum Frequency for Input DDR

t

DDRIREMCLR

2

3

t

DDRICLKQ1

J

= 70°C, Worst-Case VCC = 1.425 V

4

Description

2

R ev i si o n 1 8

3

5

t

DDRICLKQ2

t

DDRISUD

Table 2-7 on page 2-7

6

4

5

7

IGLOO Low Power Flash FPGAs

t

DDRIHD

t

for derating values.

8

DDRIRECCLR

6

7

TBD

0.48

0.65

0.50

0.40

0.00

0.00

0.82

0.98

0.00

0.23

0.19

0.31

0.28

Std.

9

Units

MHz

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

2- 95

Related parts for AGL400V5-FGG484

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

PBGA 196/FPGA, 9216 CLBS, 400000 GATES

Manufacturer:

Actel

Part Number:

Description:

FPGA - Field Programmable Gate Array 400K System Gates

Manufacturer:

Actel

Datasheet:

Part Number:

Description:

FPGA - Field Programmable Gate Array 400K System Gates

Manufacturer:

Actel

Datasheet:

Part Number:

Description:

FPGA - Field Programmable Gate Array 400K System Gates

Manufacturer:

Actel

Datasheet:

Part Number:

Description:

FPGA - Field Programmable Gate Array 400K System Gates

Manufacturer:

Actel

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Silicon Sculptor Programming Mod

Manufacturer:

Actel

Part Number:

Description:

MCU, MPU & DSP Development Tools InSystem Programming ProASICPLUS Devices

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators PQ160 Module

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators Axcelerator Adap Module Kit

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators Evaluation

Manufacturer:

Actel