XR88C681CP/40 Exar Corporation, XR88C681CP/40 Datasheet - Page 33

XR88C681CP/40

Manufacturer Part Number

XR88C681CP/40

Description

Dual Channel UART

Manufacturer

Exar Corporation

Datasheet

1.XR88C681CP40-F.pdf

(101 pages)

Specifications of XR88C681CP/40

Features

*

Number Of Channels

2, DUART

Fifo's

1 Byte, 3 Byte

Voltage - Supply

5V

With Parallel Port

Yes

With Cmos

Yes

Mounting Type

Through Hole

Package / Case

40-DIP (0.600", 15.24mm)

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XR88C681CP/40

Manufacturer:

TP

Quantity:

6 238

Part Number:

XR88C681CP/40

Manufacturer:

EXAR/艾科嘉

Quantity:

20 000

Company:

Part Number:

XR88C681CP/40-F

Manufacturer:

Linear

Quantity:

185

Direct Interrupts

The 8085 CPU inputs RST 7.5, RST 6.5, and RST 5.5 are

“Direct Interrupt” request inputs. Specifically, if any of

these inputs are asserted, then the program counter of

the CPU is, upon completion of the current instruction,

automatically

(pre-determined by the circuitry within the 8085 device),

and branches program control to that location. These

“Direct” interrupts do not provide the peripheral device

with any sort of “Interrupt Acknowledge”.

according to Table 11, if the RST 7.5 input were asserted,

the value “003C

counter of the CPU, and program control would branch to

that location in memory. The user is responsible to insure

that the correct interrupt service routine begins at that

location in memory.

The 8085 CPU offers interrupt prioritization, within the set

of Maskable Interrupts. This priority is reflected Table 11.

It should be noted that these priority levels only apply to

“pending” interrupt request. Once a particular interrupt

has “left the queue” and is being serviced by the CPU, this

Input Name

Rev. 2.11

RST 7.5

RST 6.5

RST 5.5

INTR

loaded

16

Table 11. 8085 CPU Maskable Interrupt Request Inputs and their Features

” would be loaded into the program

High Level Until Sampled

High Level Until Sampled

High Level Until Sampled

Positive Edge Triggered

with

Trigger

a

memory

location

Hence,

Priority

2

3

4

5

33

prioritization scheme no longer applies to that particular

interrupt. Consequently, it is possible that an RST 5.5

interrupt request could “interrupt” the interrupt service

routine for the higher priority RST 7.5 interrupt request.

Therefore, the user must guard against this phenomenon

in his/her firmware.

Table 11 also indicates that the 8085 CPU will support

“external” vectored interrupts.

commands that are used in external vectored interrupt

processing are identical to that presented for the 8080

CPU (see Section C.6.1.2).

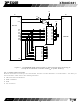

Figure 10

approaches that can be used to interface the XR88C681

DUART to the 8085 CPU.

Figure 10 presents a schematic where the DUART will

request a “Direct” RST 6.5 Interrupt to the 8085 CPU. In

this case, the Interrupt Service Routine for the DUART

must begin at 0034

simple interface technique, because there is no “Interrupt

Acknowledge” signal to route and interface.

External Vectored

Direct

Direct

Direct

Type

and

Figure 11

16

Acknowledge

in system memory. This is a very

-

INTA = “Low”

Signal?

None

None

None

XR88C681

present

The manner and

Address (Hex)

See Table 10

two

003C

002C

0034

different