PCA9546ABS,118 NXP Semiconductors, PCA9546ABS,118 Datasheet - Page 9

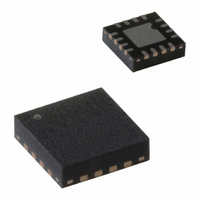

PCA9546ABS,118

Manufacturer Part Number

PCA9546ABS,118

Description

IC I2C SWITCH 4CH 16-HVQFN

Manufacturer

NXP Semiconductors

Datasheet

1.PCA9546ABS118.pdf

(25 pages)

Specifications of PCA9546ABS,118

Package / Case

16-VQFN Exposed Pad, 16-HVQFN, 16-SQFN, 16-DHVQFN

Applications

4-Channel I²C Switcher

Interface

I²C, SMBus

Voltage - Supply

2.3 V ~ 5.5 V

Mounting Type

Surface Mount

Product

Multiplexer

Number Of Lines (input / Output)

4.0 / 1.0

Propagation Delay Time

0.3 ns at 2.3 V to 5.5 V

Supply Voltage (max)

5.5 V

Supply Voltage (min)

2.3 V

Maximum Operating Temperature

+ 85 C

Minimum Operating Temperature

- 40 C

Mounting Style

SMD/SMT

Number Of Input Lines

4.0

Number Of Output Lines

1.0

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Other names

568-3378-2

935275811118

PCA9546ABS-T

935275811118

PCA9546ABS-T

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

PCA9546ABS,118

Manufacturer:

NXP/恩智浦

Quantity:

20 000

NXP Semiconductors

PCA9546A_5

Product data sheet

Fig 10. System configuration

SDA

SCL

TRANSMITTER/

RECEIVER

MASTER

7.4 Acknowledge

The number of data bytes transferred between the START and the STOP conditions from

transmitter to receiver is not limited. Each byte of eight bits is followed by one

acknowledge bit. The acknowledge bit is a HIGH level put on the bus by the transmitter,

whereas the master generates an extra acknowledge related clock pulse.

A slave receiver which is addressed must generate an acknowledge after the reception of

each byte. Also, a master must generate an acknowledge after the reception of each byte

that has been clocked out of the slave transmitter. The device that acknowledges has to

pull down the SDA line during the acknowledge clock pulse so that the SDA line is stable

LOW during the HIGH period of the acknowledge related clock pulse; set-up and hold

times must be taken into account.

A master receiver must signal an end of data to the transmitter by not generating an

acknowledge on the last byte that has been clocked out of the slave. In this event, the

transmitter must leave the data line HIGH to enable the master to generate a STOP

condition.

Fig 11. Acknowledgement on the I

RECEIVER

SLAVE

SCL from master

by transmitter

data output

by receiver

data output

TRANSMITTER/

RECEIVER

Rev. 05 — 2 July 2009

condition

START

SLAVE

S

2

C-bus

TRANSMITTER

1

MASTER

2

4-channel I

TRANSMITTER/

RECEIVER

MASTER

acknowledgement

not acknowledge

SLAVE

clock pulse for

acknowledge

8

2

C-bus switch with reset

PCA9546A

MULTIPLEXER

© NXP B.V. 2009. All rights reserved.

002aaa987

I

2

9

C-BUS

002aaa966

9 of 25