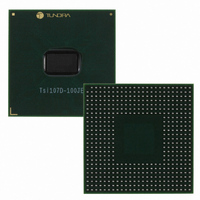

TSI107D-100JE IDT, Integrated Device Technology Inc, TSI107D-100JE Datasheet

TSI107D-100JE

Specifications of TSI107D-100JE

Available stocks

Related parts for TSI107D-100JE

TSI107D-100JE Summary of contents

Page 1

Tsi107 User Manual ™ 80C2000_MA001_05 November 2009 6024 Silver Creek Valley Road, San Jose, California 95138 Telephone: (800) 345-7015 • (408) 284-8200 • FAX: (408) 284-2775 Printed in U.S.A. ©2009 Integrated Device Technology, Inc. ® ...

Page 2

Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility ...

Page 3

Paragraph Number Audience ......................................................................................................... xxxvii Organization................................................................................................... xxxviii Suggested Reading........................................................................................... xxxix Conventions .......................................................................................................... xli Acronyms and Abbreviations .............................................................................. xlii Revision History ................................................................................................. xliii 1.1 Tsi107 PowerPC Host Bridge Features .............................................................. 1-1 1.2 Tsi107 PowerPC Host Bridge Applications ...................................................... 1-3 1.3 Tsi107 ...

Page 4

Paragraph Number 1.6.2 IEEE 1149.1 (JTAG)/Test Interface ............................................................. 1-14 Signal Descriptions and Clocking 2.1 Signal Overview ................................................................................................. 2-2 2.1.1 Signal Cross Reference................................................................................... 2-4 2.1.2 Output Signal States during Reset .................................................................. 2-6 2.2 Detailed Signal Descriptions .............................................................................. 2-8 2.2.1 60x Processor ...

Page 5

Paragraph Number 2.2.1.16.1 Transfer Acknowledge (TA)—Output.................................................. 2-17 2.2.1.16.2 Transfer Acknowledge (TA)—Input .................................................... 2-17 2.2.1.17 Local Bus Slave Claim (LBCLAIM)—Input ........................................... 2-18 2.2.1.18 Data Bus Grant Local Bus Slave (DBGLB)—Output.............................. 2-18 2.2.2 PCI Interface Signals .................................................................................... 2-18 2.2.2.1 PCI Bus Request ...

Page 6

Paragraph Number 2.2.2.15 ID Select (IDSEL)—Input........................................................................ 2-27 2.2.3 Memory Interface Signals............................................................................. 2-27 2.2.3.1 Row Address Strobe (RAS[0:7])—Output............................................... 2-27 2.2.3.2 Column Address Strobe (CAS[0:7])—Output.......................................... 2-28 2.2.3.3 SDRAM Command Select (CS[0:7])—Output ........................................ 2-28 2.2.3.4 SDRAM Data Input/Output Mask (DQM[0:7])—Output ........................ 2-28 2.2.3.5 ...

Page 7

Paragraph Number 2.2.6.3 Machine Check (MCP)—Output.............................................................. 2-39 2.2.6.4 Transfer Error Acknowledge (TEA)—Output.......................................... 2-40 2.2.6.5 Nonmaskable Interrupt (NMI)—Input ..................................................... 2-40 2.2.6.6 Quiesce Request (QREQ)—Input............................................................. 2-40 2.2.6.7 Quiesce Acknowledge (QACK)—Output ................................................ 2-41 2.2.6.8 Watchpoint Trigger Signals...................................................................... 2-41 2.2.6.8.1 Watchpoint Trigger In (TRIG_IN)—Input........................................... ...

Page 8

Paragraph Number 3.3.3 Address Translation Registers ...................................................................... 3-15 3.3.3.1 Local Memory Base Address Register (LMBAR) ................................... 3-16 3.3.3.2 Inbound Translation Window Register (ITWR)....................................... 3-16 3.3.3.3 Outbound Memory Base Address Register (OMBAR) ............................ 3-17 3.3.3.4 Outbound Translation Window Register (OTWR)................................... 3-18 ...

Page 9

Paragraph Number 4.6.1.4 Extended Memory Ending Address Register 1 and 2 —0x98 and 0x9C 4-29 4.6.2 Memory Bank Enable Register—0xA0........................................................ 4-30 4.6.3 Memory Page Mode Register—0xA3 .......................................................... 4-31 4.7 Processor Interface Configuration Registers .................................................... 4-32 4.7.1 Processor Interface Configuration Register ...

Page 10

Paragraph Number 5.3.3.3 Burst Ordering During Data Transfers ..................................................... 5-12 5.3.3.4 Effect of Alignment on Data Transfers—64-bit Data Bus ....................... 5-13 5.3.3.5 Effect of Alignment on Data Transfers—32-Bit Data Bus ...................... 5-15 5.3.4 Address Transfer Termination ...................................................................... 5-17 5.3.4.1 Tsi107 ...

Page 11

Paragraph Number 6.2.13 Processor-to-SDRAM Transaction Examples .............................................. 6-38 6.2.14 PCI-to-SDRAM Transaction Examples........................................................ 6-44 6.3 FPM or EDO DRAM Interface Operation........................................................ 6-48 6.3.1 Supported FPM or EDO DRAM Organizations ........................................... 6-50 6.3.2 FPM or EDO DRAM Address Multiplexing................................................ 6-52 6.3.2.1 Row ...

Page 12

Paragraph Number 7.2.1.2 DMA-Initiated Transactions to the PCI Bus .............................................. 7-6 7.2.2 PCI Bus Arbiter Operation ............................................................................. 7-7 7.2.3 PCI Bus Parking ............................................................................................. 7-8 7.2.4 Power-Saving Modes and the PCI Arbiter ..................................................... 7-9 7.2.5 Broken Master Lock-Out ................................................................................ 7-9 7.3 ...

Page 13

Paragraph Number 7.7.4 PCI Address Translation Support ................................................................. 7-35 7.7.4.1 Inbound PCI Address Translation ............................................................ 7-35 7.7.4.2 Outbound PCI Address Translation.......................................................... 7-35 7.7.4.3 Initialization Code Translation in Agent Mode ........................................ 7-36 8.1 DMA Overview .................................................................................................. 8-1 8.2 DMA Register Summary ...

Page 14

Paragraph Number 8.7.3 Current Descriptor Address Registers (CDARs) .......................................... 8-20 8.7.4 Source Address Registers (SARs) ................................................................ 8-21 8.7.5 Destination Address Registers (DARs) ........................................................ 8-22 8.7.6 Byte Count Registers (BCRs) ....................................................................... 8-23 8.7.7 DAR and BCR Values—Double PCI Write ................................................. 8-23 ...

Page 15

Paragraph Number 9.3.4.2.6 Inbound Post_FIFO Tail Pointer Register (IPTPR) ............................. 9-21 9.3.4.2.7 Outbound Free_FIFO Head Pointer Register (OFHPR)....................... 9-22 9.3.4.2.8 Outbound Free_FIFO Tail Pointer Register (OFTPR) ......................... 9-23 9.3.4.2.9 Outbound Post_FIFO Head Pointer Register (OPHPR)....................... 9-23 9.3.4.2.10 Outbound Post_FIFO Tail ...

Page 16

Paragraph Number 10.4.8 Interrupt Service Routine Flowchart........................................................... 10-17 Embedded Programmable Interrupt Controller (EPIC) Unit 11.1 EPIC Unit Overview ......................................................................................... 11-1 11.1.1 EPIC Features Summary............................................................................... 11-2 11.1.2 EPIC Interface Signal Description................................................................ 11-2 11.1.3 EPIC Block Diagram .................................................................................... 11-3 11.2 EPIC Register ...

Page 17

Paragraph Number 11.9.7.5 Global Timer Destination Registers (GTDRs) ....................................... 11-25 11.9.8 External (Direct and Serial), and Internal Interrupt Registers .................... 11-26 11.9.8.1 Direct & Serial Interrupt Vector/Priority Registers (IVPRs, SVPRs).... 11-26 11.9.8.2 Direct & Serial Interrupt Destination Registers (IDRs, SDRs) ...

Page 18

Paragraph Number 13.2.2 Processor Bus Error Signals ........................................................................ 13-3 13.2.2.1 Machine Check (MCP) ............................................................................. 13-3 13.2.2.2 Transfer Error Acknowledge (TEA)......................................................... 13-4 13.2.3 PCI Bus Error Signals................................................................................... 13-5 13.2.3.1 System Error (SERR) ............................................................................... 13-5 13.2.3.2 Parity Error (PERR).................................................................................. 13-5 13.2.3.3 Nonmaskable ...

Page 19

Paragraph Number 14.3.4.3 SDRAM Paging during Sleep Mode ........................................................ 14-7 14.4 Example Code Sequence for Entering Processor and Tsi107 Sleep Modes..... 14-7 15.1 Debug Register Summary ................................................................................. 15-1 15.2 Memory Data Path Error Injection/Capture...................................................... 15-2 15.2.1 Memory Data Path Error ...

Page 20

Paragraph Number B.1 Byte Ordering Overview..................................................................................... B-1 B.2 Byte-Ordering Mechanisms ................................................................................ B-1 B.3 Big-Endian Mode................................................................................................ B-2 B.4 Little-Endian Mode............................................................................................. B-5 B.4.1 I/O Addressing in Little-Endian Mode ......................................................... B-15 B.5 Setting the Endian Mode of Operation ............................................................. B-15 C.1 Example PowerPC ...

Page 21

Figure Number 1-1 System Using Tsi107 as a Host Bridge ........................................................................ 1-3 1-2 Embedded System Using the Tsi107 as a Bridge ......................................................... 1-4 1-3 Embedded System Using Tsi107 with a Distributed I/O Processor ............................. 1-5 1-4 Multiprocessor System Using the ...

Page 22

Figure Number 4-12 Extended Memory Starting Address Register 1—0x88. ............................................ 4-27 4-13 Extended Memory Starting Address Register 2—0x8C............................................. 4-28 4-14 Memory Ending Address Register 1—0x90............................................................... 4-28 4-15 Memory Ending Address Register 2—0x94............................................................... 4-29 4-16 Extended Memory Ending Address Register 1—0x98............................................... ...

Page 23

Figure Number 6-10 SDRAM Single Beat Write Timing (SDRAM Burst Length = 4).............................. 6-25 6-11 SDRAM Four-Beat Burst Write Timing—64-Bit Mode ............................................ 6-26 6-12 SDRAM Eight-Beat Burst Write Timing—32-Bit Mode........................................... 6-26 6-13 SDRAM Mode Register Set Timing........................................................................... 6-27 6-14 Registered ...

Page 24

Figure Number 6-53 ROM/Flash Address Multiplexing—32-Bit Extended Mode ..................................... 6-81 6-54 ROM/Flash Address Multiplexing—64-Bit Extended Mode ..................................... 6-82 6-55 Read Access Timing for Non-Burst ROM/Flash Devices in 32- or 64-Bit Mode ..... 6-84 6-56 Read Access Timing (Cache Block) for ...

Page 25

Figure Number 9-4 Extended Doorbell Mask Register (EDBMR) .............................................................. 9-5 9-5 Extended Doorbell Status Register (EDBSR) .............................................................. 9-6 9-6 Extended Doorbell Write 1 Clear Register (EDBW1C) ............................................... 9-6 9-7 Extended Doorbell Write 1 Set Register (EDBW1S) ................................................... 9-7 9-8 I ...

Page 26

Figure Number 11-15 Global Timer Destination Register (GTDR) ............................................................ 11-26 11-16 Direct and Serial Interrupt Vector/Priority Registers (IVPR and SVPR)................. 11-27 11-17 Direct and Serial Destination Registers (IDR and SDR) .......................................... 11-28 11-18 Processor Current Task Priority Register (PCTPR) ................................................. ...

Page 27

Figure Number 16-10 Watchpoint #2 Address Mask Register (WP2_ADDR_MASK) — Offsets 0xF_F03C, 0xF3C 16-8 16-11 Watchpoint Control Register (WP_CONTROL) — Offsets 0xF_F048, 0xF48 ........ 16-9 16-12 Watchpoint Facility State Diagram........................................................................... 16-13 16-13 Watchpoint Facility Block Diagram ......................................................................... 16-14 A-1 Processor ...

Page 28

Figure Number xxx ILLUSTRATIONS Title Tsi107 PowerPC Host Bridge User Manual Page Number IDT ...

Page 29

Table Number i Acronyms and Abbreviated Terms .............................................................................. xlii 1-1 Tsi107 Power Modes Summary.................................................................................. 1-13 2-1 Tsi107 Signal Cross Reference..................................................................................... 2-4 2-2 Output Signal States During System Reset................................................................... 2-7 2-3 60x Interface Data Bus Byte Lane Assignments ........................................................ 2-15 2-4 ...

Page 30

Table Number 4-16 Power Management Configuration Register 2—0x72................................................ 4-20 4-17 Output Driver Control Register Bit Definitions—0x73 ............................................. 4-22 4-18 CLK Driver Control Register Bit Definitions—0x74................................................. 4-23 4-19 Miscellaneous I/O Control Register Bit Definitions—0x76....................................... 4-25 4-20 Embedded Utilities Memory Base Address ...

Page 31

Table Number 6-7 SDRAM Address Multiplexing SDBA[1:0] and SDMA[12:0]—64-Bit Mode ......... 6-12 6-8 Memory Data Path Parameters ................................................................................... 6-15 6-9 SDRAM System Configurations ................................................................................ 6-15 6-10 Tsi107 SDRAM Interface Commands........................................................................ 6-19 6-11 SDRAM Interface Timing Intervals ........................................................................... 6-23 6-12 The ...

Page 32

Table Number 9-7 EDBSR Field Descriptions—Offsets 0x078, 0x0_0078............................................... 9-6 9-8 EDBW1C Field Descriptions—Offsets 0x080, 0x0_0080 ........................................... 9-7 9-9 EDBW1S Field Descriptions—Offsets 0x088, 0x0_0088 ........................................... 9-7 9- PCI Configuration Identification Register Settings ............................................... 9 Register ...

Page 33

Table Number 11-14 EUMBBAR Offsets for GTBCRs............................................................................. 11-23 11-15 GTBCR Field Descriptions....................................................................................... 11-24 11-16 EUMBBAR Offsets for GTVPRs............................................................................. 11-24 11-17 GTVPR Field Descriptions ....................................................................................... 11-25 11-18 EUMBBAR Offsets for GTDRs ............................................................................... 11-25 11-19 GTDR Field Descriptions ......................................................................................... 11-26 11-20 EUMBBAR ...

Page 34

Table Number xxxvi TABLES Title Tsi107 PowerPC Host Bridge User Manual Page Number IDT ...

Page 35

About This Book The primary objective of this user’s manual is to describe the functionality of the Tsi107 PowerPC host bridge. The Tsi107 is one device in a family of products that provide system-level support for industry-standard interfaces to be ...

Page 36

Organization Following is a list describing the major sections of this manual: • Chapter 1, “Overview,” is for readers who want a general understanding of the features and functions of the Tsi107 device and its component parts. • Chapter 2, ...

Page 37

Chapter 16, “Programmable I/O and Watchpoint,” describes the capabilities of the TRIG_IN signal, and how the TRIG_OUT signal can be generated based on programmable watchpoints on the 60x bus. • Appendix A, “Address Map A.” The Tsi107 supports two ...

Page 38

Computer Organization and Design: The Hardware/Software Interface, Second Edition, by David A. Patterson and John L. Hennessy • Inside Macintosh: RISC System Software, Addison-Wesley Publishing Company, One Jacob Way, Reading, MA, 01867; Tel. (800) 282-2732 (U.S.A.), (800) 637-0029 (Canada), ...

Page 39

PowerPC Microprocessor Family: The Programmer’s Reference Guide: MPCPRG/D (Motorola order #) is a concise reference that includes the register summary, memory control model, exception vectors, and the PowerPC instruction set. • PowerPC Microprocessor Family: The Programmer’s Pocket Reference Guide: ...

Page 40

OR logical operator || Concatenate logical operator Indicates reserved bits or bit fields in a register. Although these bits may be written to as either ones or zeros, they are always read as zeros. Acronyms ...

Page 41

Table i. Acronyms and Abbreviated Terms<Emphasis> (Continued) Term Mux Multiplex No-op No operation PCI Peripheral component interconnect PICR Processor interface configuration register PLL Phase-locked loop PMC Power management controller PMCR Power management configuration register RAS Row address strobe RISC Reduced ...

Page 42

... Added a note about the LBCLAIM signal that is applicable to designs that are migrating from the Tsi107C to the Tsi107D (see Section 5.6, “60x Local Bus Slave Support” on page 5-24). • Added a list of ways that a processor-initiated PCI read transaction that is retried on the PCI bus can be terminated (see Section 7.2.1.1, “ ...

Page 43

Chapter 1 Overview This chapter provides an overview of the Tsi107 PowerPC host bridge for high-performance embedded systems. The Tsi107 is a cost-effective, general-purpose PowerPC host bridge telecommunications, and other embedded markets. It can be used for in applications such ...

Page 44

PCI interface operating MHz — PCI 2.1-compliant — PCI 5.0-V tolerance — Support for PCI locked accesses to memory — Support for accesses to PCI memory, I/O, and configuration spaces — Selectable big- or little-endian ...

Page 45

Dynamic power management—Supports 60x nap, doze, and sleep modes • Programmable input and output signals with watchpoint capability • Debug features — Error injection/capture on data path — IEEE 1149.1 (JTAG)/test interface • Processor interface — Supports up to ...

Page 46

With the embedded enhancements provided in the Tsi107 possible to use it in peripheral processor applications as shown in Figure 1-2. PCI Bus Peripheral 1 Peripheral 2 Tsi107 DMA MU EPIC PowerPC Microprocessor ...

Page 47

PCI Bus Peripheral Peripheral 2 1 Local PCI Bus Tsi107 DMA MU(I O) Peripheral 2 Logic EPIC PowerPC Microprocessor Figure 1-3. Embedded System Using Tsi107 with a Distributed I/O Processor The processor bus interface (60x) of the ...

Page 48

PowerPC Microprocessor 60x bus Tsi107 Local bus slave Figure 1-4. Multiprocessor System Using the Tsi107 and a Local Bus Slave 1.3 Tsi107 Major Functional Blocks The Tsi107 integrates a PCI bridge, memory controller, DMA controller, EPIC interrupt controller/timers, a message ...

Page 49

Message Unit ( DMA Master Slave Five IRQs/ EPIC Interrupt 16 Serial Controller Interrupts Timers IEEE1149.1 JTAG Boundary Scan 80C2000_BK001_01 1.3.1 60x Processor Interface The Tsi107 supports a programmable interface to a variety of PowerPC ...

Page 50

Depending on the system implementation, the processor bus may operate at the PCI bus clock rate multiple of the PCI bus clock rate (determined at reset). The 60x processor bus is synchronous, with all timing relative to ...

Page 51

The Tsi107’s PCI interface can be configured as host or agent. In host mode, the interface acts as the main memory controller for the system and responds to all host memory transactions. In agent mode, the Tsi107 can be configured ...

Page 52

PCI Agent Capability In certain applications, the embedded system architecture dictates that the Tsi107 bridges to a peripheral processor. In this case, the peripheral logic must not act like a host bridge for the PCI bus. Instead it functions ...

Page 53

Extended Doorbell Register Facility The Tsi107 MU also contains an extended doorbell register mechanism that facilitates interprocessor communication through interrupts in a dual-local-processor system. For example, processor 0 can write to the EDBW1S register to generate an interrupt to ...

Page 54

Embedded Programmable Interrupt Controller (EPIC) The integrated embedded programmable interrupt controller (EPIC) of the Tsi107 reduces the overall component count in embedded applications. The EPIC unit is designed to collect external and internal hardware interrupts, prioritize them, and deliver ...

Page 55

The peripheral processor (60x) bus clock frequency on the CPU_CLK[0:2] outputs is configured at reset (by the Tsi107 PLL configuration signals (PLL_CFG[0:3])) ...

Page 56

Programmable I/O Signals with Watchpoint The Tsi107 programmable I/O facility allows the system designer to monitor the 60x bus two watchpoints and their respective 4-bit countdown values can be programmed. When the programmed threshold of the selected ...

Page 57

Chapter 2 Signal Descriptions and Clocking This chapter provides descriptions of the Tsi107’s external signals. It describes each signal’s behavior when the signal is asserted and negated and when the signal is an input or an output. A bar over ...

Page 58

Signal Overview The Tsi107’s signals are grouped as follows: • 60x processor interface • PCI interface signals • Memory interface signals • EPIC control signals 2 • interface signals • System control, power management, and local bus ...

Page 59

GNT[4:0] REQ[4:0] AD[31:0] PAR C/BE[3:0] DEVSEL FRAME PCI IRDY Interface LOCK TRDY PERR SERR STOP INTA IDSEL RAS[0:7]/CS[0:7] CAS[0:7]/DQM[0:7] WE SDMA[13:0] SDBA1 SDBA0 MDH[0:31] Memory MDL[0:31] Interface PAR[0:7]/AR[19:12] CKE SDRAS SDCAS RCS[0:3] FOE AS IRQ0/S_INT IRQ1/S_CLK IRQ2/S_RST EPIC Control IRQ3/S_FRAME ...

Page 60

Signal Cross Reference The following sections are intended to provide a quick summary of signal functions. Table 2-1 provides an alphabetical cross-reference to the signals of the Tsi107. It details the signal name, interface, alternate functions, number of signals, ...

Page 61

Table 2-1. Tsi107 Signal Cross Reference<Emphasis> (Continued) Signal Signal Name INT 60x interrupt request INTA Interrupt request IRDY Initiator ready IRQ0 Interrupt 0 IRQ1 Interrupt 1 IRQ2 Interrupt 2 IRQ3 Interrupt 3 IRQ4 Interrupt 4 L_INT Local interrupt LBCLAIM Local ...

Page 62

Table 2-1. Tsi107 Signal Cross Reference<Emphasis> (Continued) Signal Signal Name SDCAS SDRAM column access strobe SDMA[13:0] SDRAM address 13–0 1 SDMA[10:1] SDRAM_CLK[0:3] SDRAM clock outputs SDRAM_SYNC_OUT SDRAM clock output SDRAM_SYNC_IN SDRAM feedback clock SDRAS SDRAM row address strobe Memory SERR ...

Page 63

There are 18 signals that serve alternate functions as reset configuration input signals during system reset. Their default values and the interpretation of their voltage levels during reset are described in Section 2.4, “Configuration Signals Sampled at ...

Page 64

Detailed Signal Descriptions The following subsections describe the Tsi107 input and output signals, the meaning of their different states, and relative timing information for assertion and negation. In cases where signals serve multiple functions (and have multiple names), they ...

Page 65

Negation—Occurs when other higher priority transactions are pending. 2.2.1.3 Address Bus (A[0:31]) The address bus (A[0:31]) consists of 32 signals that are both input and output signals. 2.2.1.3.1 Address Bus (A[0:31])—Output Following are the state meaning and timing comments for ...

Page 66

Negation—Occurs one clock cycle after assertion. High-impedance—Occurs one clock cycle after the assertion of AACK. 2.2.1.4.2 Transfer Start (TS)—Input Following are the state meaning and timing comments for the TS input signal. State Meaning Asserted—Indicates that ...

Page 67

Transfer Type (TT[0:4])—Input Following are the state meaning and timing comments for TT[0:4] as input signals. State Meaning Asserted/Negated—Specifies the type of 60x bus transfer in progress. Refer to Section 5.3.3.1, “Transfer Type Signal Encodings,” for transfer type encodings. ...

Page 68

State Meaning Asserted—Indicates that a burst transfer is in progress. Negated—Indicates that a burst transfer is not in progress. Timing Comments Assertion/Negation—The same as A[0:31]. High-impedance—The same as A[0:31]. 2.2.1.7.2 Transfer Burst (TBST)—Input Following are the state meaning and timing ...

Page 69

Negated—Indicates that an access is not global and that hardware-enforced coherency is not required. Timing Comments Assertion/Negation—The same as A[0:31]. High-impedance—The same as A[0:31]. 2.2.1.11 Address Acknowledge (AACK)—Output The address acknowledge (AACK) signal is an output signal on the Tsi107. ...

Page 70

Negation/High-impedance—ARTRY is released to high-impedance for the first half of the second clock cycle after the assertion of AACK, then it is negated for one clock and released to high-impedance. 2.2.1.12.2 Address Retry (ARTRY)—Input Following are the state meaning and ...

Page 71

Data Bus (DH[0:31], DL[0:31]) The data bus (DH[0:31], DL[0:31]) consists of 64 signals that are both input and output signals on the Tsi107. The data bus is comprised of two halves—data bus high (DH[0:31]) and data bus low (DL[0:31]). ...

Page 72

Data Bus (DH[0:31], DL[0:31])—Input Following are the state meaning and timing comments for the data bus as input signals. State Meaning Asserted/Negated—Represents the state of data being driven by a 60x processor or local bus slave. Timing Comments Assertion/Negation—For ...

Page 73

High-impedance—the data parity signals are released to high-impedance one clock cycle after the last assertion of TA. If the address tenure is ARTRYd, the data parity signals high-impedance state one clock cycle after the qualified ARTRY. 2.2.1.16 ...

Page 74

Local Bus Slave Claim (LBCLAIM)—Input The local bus slave claim (LBCLAIM) signal is an input on the Tsi107. Following are the state meaning and timing comments for the LBCLAIM signal. See Section 5.6, “60x Local Bus Slave Support,” for ...

Page 75

PCI Bus Request (REQ[4:0])—Internal Arbiter Enabled The Tsi107 PCI arbiter is enabled by a low value on the reset configuration pin SDMA9 or by the setting of bit 15 of the PCI arbitration control register. In this case, the ...

Page 76

GNTn signal during any clock cycle. Negated—Indicates that the Tsi107 has not granted control of the PCI bus and external devices may not initiate a PCI transaction. 2.2.2.2.2 PCI Bus Grant (GNT[4:0])—Internal Arbiter Disabled The Tsi107 PCI arbiter is disabled ...

Page 77

Parity (PAR) The PCI parity (PAR) signal is both an input and output signal on the Tsi107. See Section 7.6.1, “PCI Parity,” for more information on PCI parity. 2.2.2.4.1 Parity (PAR)—Output Following is the state meaning for PAR as ...

Page 78

Table 2-4. PCI Command Encodings C/BE[3:0] 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 1 The Tsi107 does not generate this command or the reserved commands. 2.2.2.5.2 Command/Byte Enable (C/BE[3:0])—Input Following is ...

Page 79

Device Select (DEVSEL)—Input Following is the state meaning for DEVSEL as an input signal. State Meaning Asserted—Indicates that some PCI target (other than the Tsi107) has decoded its address as the target of the current access. This is useful ...

Page 80

During a read, the Tsi107 negates IRDY to insert a wait cycle when it cannot accept data from the target. 2.2.2.8.2 Initiator Ready (IRDY)—Input Following is the state meaning for IRDY as ...

Page 81

Target Ready (TRDY)—Input Following is the state meaning for TRDY as an input signal. State Meaning Asserted—Indicates another PCI target is able to complete the current data phase of a transaction. If the Tsi107 is the initiator of the ...

Page 82

System Error (SERR)—Output Following is the state meaning for SERR as an output signal. State Meaning Asserted—Indicates that an address parity error, a target-abort (when the Tsi107 is acting as the initiator), or some other system error (where the ...

Page 83

ID Select (IDSEL)—Input Following is the state meaning for IDSEL. See Section 7.3.3.3, “Configuration Space Addressing,” for more information about the role of the IDSEL signal in PCI configuration transactions. State Meaning Asserted—When the C/BE[3:0] encoding is set to ...

Page 84

Column Address Strobe (CAS[0:7])—Output The eight column address strobe (CAS[0:7]) signals are outputs on the Tsi107. CAS0 connects to the most-significant byte select. CAS7 connects to the least-significant byte select. When the Tsi107 is operating in 32-bit mode (see ...

Page 85

Write Enable (WE)—Output The write enable (WE) signal is an output on the Tsi107. For SDRAM part of the SDRAM command encoding. See Section 6.2, “SDRAM Interface Operation,” for more information. Following are the state meaning and ...

Page 86

State Meaning Asserted/Negated—Selects the SDRAM internal bank to be activated during the row address phase and selects the SDRAM internal bank for the read or write operation during the column address phase of the memory access. See Section 6.2.2, “SDRAM ...

Page 87

Memory Data Bus (MDH[0:31], MDL[0:31])—Output Following are the state meaning and timing comments for the memory data bus as output signals. State Meaning Asserted/Negated—Represents the value of data being driven by the Tsi107. Timing Comments Assertion/Negation—For DRAM accesses, the ...

Page 88

Data Parity (PAR[0:7])—Input Following are the state meaning and timing comments for PAR[0:7] as input signals. State Meaning Asserted/Negated—Represents the byte parity or ECC bits being read from memory (PAR0 is the most-significant parity bit and corresponds to byte ...

Page 89

State Meaning Asserted/Negated—SDRAS is part of the SDRAM command encoding and is used for SDRAM bank selection during read or write operations. See Section 6.2, “SDRAM Interface Operation,” for more information. Timing Comments Assertion—SDRAS is valid on the rising edge ...

Page 90

Flash. 34 Tsi107 PowerPC Host Bridge User Manual IDT ...

Page 91

Timing Comments Assertion—The Tsi107 asserts FOE at the start of the Flash read cycle. Negation—Controlled by the ROMFAL and ROMNAL parameters of the MCCR1 register. 2.2.3.16 Address Strobe (AS)—Output The AS output signal is used as a user-defined timing signal ...

Page 92

Serial Interrupt Stream (S_INT)—Input This signal represents the incoming interrupt stream in serial interrupt mode. State Meaning Asserted/Negated—Represents the interrupts for external interrupt sources with individually programmable sense and polarity. These interrupts are clocked in to ...

Page 93

I C Interface Control Signals These two signals serve as a communication interconnect with other devices. All devices connected to these two signals must have open-drain or open-collector outputs. The logic AND function is performed on both of ...

Page 94

Hard Reset There are two hard reset signals on the Tsi107. The HRESET input signal causes the Tsi107 to abort all current internal and external transactions and set all registers to their default values. The HRESET_CPU output signal is ...

Page 95

Soft Reset (SRESET)—Output The assertion of the soft reset output signal is caused by writing a one to the PI register in the EPIC unit. A soft reset is recoverable, provided that in attempting to reach a recoverable state, ...

Page 96

Transfer Error Acknowledge (TEA)—Output The transfer error acknowledge (TEA) signal is an output on the Tsi107. Note that the TEA signal can be disabled by clearing the TEA_EN bit in processor interface configuration register 1 (PICR1). Following are the ...

Page 97

Quiesce Acknowledge (QACK)—Output The quiesce acknowledge (QACK) signal is an output on the Tsi107. See Chapter 14, “Power Management,” for more information about the power management signals. Following are the state meaning and timing comments for the QACK output ...

Page 98

Test and Configuration Signals The Tsi107 has several signals that are sampled during reset to determine the configuration of the ROM, Flash, and dynamic memory, and the phase-locked loop clock mode. To facilitate system testing, the Tsi107 provides a ...

Page 99

JTAG Test Data Output (TDO)—Output Following is the state meaning for the TDO output signal. State Meaning Asserted/Negated—The contents of the selected internal instruction or data register are shifted out onto this signal on the falling edge of TCK. ...

Page 100

PCI Clock (PCI_CLK[0:4])—Output These signals provide multiple copies of OSC_IN as output signals when using the PCI clock fanout buffer feature. If these outputs are not needed, they can be individually disabled in the CDCR register to minimize power ...

Page 101

CPU Clock 0–2 (CPU_CLK[0:2])—Output The CPU_CLK[0:2] signals can be connected to the clock inputs two processors and other logic on the 60x bus interface. These clock signals operate at the same frequency as the SDRAM_CLKn outputs, ...

Page 102

Tsi107 OSC_IN Figure 2-2. Clock Subsystem Block Diagram The sys_logic_clk signal may be set to a multiple of the PCI bus frequency as defined in the Tsi107 Hardware Specification. To help reduce the amount of discrete logic required in a ...

Page 103

The supported settings for the PLL configuration pins are defined in the Tsi107 Hardware Specifications. 2.3.2 DLL Operation and Locking The DLL on the Tsi107 generates the SDRAM_CLK[0:3], SDRAM_SYNC_OUT, ...

Page 104

SDRAM_CLK[0:3] signals (shown in Figure 2-4), PCI_SYNC_IN must be phase-aligned with the input to the external PLL, and the Tsi107 system logic PLL should be programmed to have the ...

Page 105

OSC Figure 2-5. Clocking Solution—Small Load Requirements Tsi107 OSC_IN Figure 2-6. Clocking Solution—High Clock Fanout Required Figure 2-7 shows a fourth example clocking scenario, where all the clocks (including the CPU clocks) are generated externally. In this case, the delay ...

Page 106

Tsi107 OSC_IN Figure 2-7. Clocking Solution—High Clock Fanout with External CPU Clocks 2.4 Configuration Signals Sampled at Reset Table 2-6 contains a description of the signals sampled for configuration at the negation of the HRESET. Note that throughout this manual, ...

Page 107

Table 2-6. Tsi107 Reset Configuration Signals Signal Name(s) Default MDL[0], FOE 11 Sets the initial ROM bank 0 data path width, DBUS_SIZE[0:1], values in MCCR1. DBUS_SIZE[0:1] = (MDL[0], FOE) at reset. MDL[0] also selects the size of the 60x data ...

Page 108

Table 2-6. Tsi107 Reset Configuration Signals<Emphasis> (Continued) Signal Name(s) Default SDMA5 1 Driver capability for SDA, SCL, CKO, QACK, and MCP as well as 60x output signals (shown in Table 2-2). The value of this signal sets the initial value ...

Page 109

Chapter 3 Address Maps The Tsi107 in PCI host mode supports two address mapping configurations designated as address map A, and address map B. The address map is selected at reset by the SDBA0 configuration pin. The address map selected ...

Page 110

Address Map B The address space of map B is divided into four areas—local memory, PCI memory, PCI I/O, and system ROM space. Throughout this chapter, the term local memory is used to mean that (S)DRAM is directly controlled ...

Page 111

Table 3-2. Address Map B—PCI Memory Master View in Host Mode PCI Memory Transaction Address Range Hex 0000_0000 3FFF_FFFF 0 4000_0000 77FF_FFFF 1G 7800_0000 7BFF_FFFF 2G - 128M 7C00_0000 7FFF_FFFF 2G - 64M 8000_0000 FDFF_FFFF 2G FE00_0000 FEFF_FFFF 4G - ...

Page 112

The processor address range 0xFE01_0000–0xFE7F_FFFF is reserved for future use. 5. The Tsi107 forwards processor transactions in this range to the PCI I/O space with the 8 most significant bits cleared (that is, AD[31:0] = 0x00 ...

Page 113

Processor 0 Local memory space Local memory cycles 1GB 2GB - 128MB 64-bit extended ROM 2GB PCI memory space 4GB - 32MB PCI I/O space 4GB - 32MB + 64KB 4GB - 24MB PCI I/O space 4GB - 20MB CONFIG_ADDR ...

Page 114

PCI Master Memory Space 0 Local memory space 0 to 1GB 1GB 2GB - 128M Extended ROM 2GB PCI memory addresses in 2GB to 2GB - 48MB range 4GB - 16M ROM (read only) 4GB Figure 3-2. PCI Memory Master ...

Page 115

PCI Master I/O Space Addressable by local processor Reserved Addressable by local processor Not addressable by local processor Figure 3-3. PCI I/O Master Address Map B IDT Memory Controller 0 64KB 8MB 12MB Tsi107 does not respond as a target ...

Page 116

Address Map B Options When configured for address map B and host mode, the Tsi107 supports four optional address mappings by programming the AMBOR register; see Section 4.9, “Address Map B Options Register—0xE0.” The options available are as follows: ...

Page 117

Processor Compatibility Hole and Alias Space Table 3-5 defines the optional processor compatibility hole and processor alias space and how they fit into map B. Table 3-5. Address Map B—Processor View in Host Mode Options Processor Core Address Range ...

Page 118

PCI Memory Space 0 640 KB Processor Compatibility Hole 768 Figure 3-4. Address Map B Processor Options in Host Mode 3.2.2 PCI Compatibility Hole and Alias Space Table 3-6 defines the optional PCI compatibility hole and ...

Page 119

Table 3-6. Address Map B—PCI Memory Master View in Host Mode Options<Emphasis> PCI Memory Transaction Address Range Hex FD00_0000 FDFF_FFFF 4G - 48M FE00_0000 FEFF_FFFF 4G - 32M 1. This address range is separately programmable (see Section 4.9, “Address Map ...

Page 120

PCI (outbound) transactions. Note that address translation is supported only for agent mode not supported when the Tsi107 is operating in host mode. Also note that since agent mode is supported only for address map B, ...

Page 121

PCI Memory Space 0 Local memory base address Inbound memory window 4G Figure 3-6. Inbound PCI Address Translation Inbound address translation only allows address translation to the local memory space (the lower 1 Gbyte of the address space). This ...

Page 122

Outbound PCI Address Translation For outbound translation, an outbound memory window is specified in the upper 2 Gbytes of the Tsi107’s address space, and an outbound translation window is specified in the PCI memory space. Local processor and DMA ...

Page 123

The outbound memory base address register (OMBAR) and the outbound translation window register (OTWR) specify the location and size of the outbound memory window and the outbound translation window. These registers are described in Section 3.3.3, “Address Translation Registers.” Outbound ...

Page 124

Local Memory Base Address Register (LMBAR) The LMBAR, shown in Figure 3-8 and Table 3-8, defines the inbound memory window. Reserved Inbound Memory Base Address 31 Figure 3-8. Local Memory Base Address Register (LMBAR)—0x10 Table 3-8. Bit Settings for ...

Page 125

Table 3-9. Bit Settings for ITWR—0x0_2310 Reset Bits Name Value 31 — 0 30–12 Inbound Undefined translation base address 11–5 — All 0s 4–0 Inbound All 0s window size The lower-order address bits of the base address field of ITWR ...

Page 126

Table 3-10. Bit Settings for OMBAR—0x0_2300 Reset Bits Name Value 31 — 1 30–12 Outbound Undefined memory base address 11 – 0 — All 0s 3.3.3.4 Outbound Translation Window Register (OTWR) The OTWR, shown in Figure 3-11 and Table 3-11, ...

Page 127

Table 3-11. Bit Settings for OTWR—0x0_2308<Emphasis> (Continued) Bits Name Reset Value R/W 4–0 Outbound All 0s window size The lower-order address bits of the base address field of OTWR that are within the range specified by the window size are ...

Page 128

Registers—LMBAR and PCSRBAR.” Note that the EUMB should not reside inside either the outbound memory window or the outbound translation window. Operation is not guaranteed if the two are overlapping. Note that the processor must not run transactions to the ...

Page 129

Table 3-12 summarizes the embedded utilities local memory registers and their offsets. Table 3-12. Embedded Utilities Local Memory Register Summary Local Memory Offset Register Set 0x0_0000 - 0x0_0FFF Message registers, Doorbell interface, I 0x0_1000 – 0x0_1FFF DMA controller 0x0_2000 – ...

Page 130

PCI Memory Space 0 PCSRBAR PCSRBAR+4KB-1 4G Figure 3-13. Embedded Utilities Memory Block Mapping to PCI Memory Table 3-13 summarizes the embedded utilities registers accessible by the PCI bus and their offsets. Table 3-13. Embedded Utilities Peripheral Control and Status ...

Page 131

Chapter 4 Configuration Registers This chapter describes the programmable configuration registers of the Tsi107. These registers are generally set up by initialization software following a power-on reset, hard reset, or error handling routines. All the internal registers of the Tsi107 ...

Page 132

A subset of the configuration registers is accessible from the PCI bus through the use of PCI configuration transactions. The Tsi107 responds to standard PCI configuration transactions when its IDSEL signal is asserted. Table 4-3 provides a listing of configuration ...

Page 133

Code sequence: stw r0,0(r1) sync stb r3,2(r2) sync Results:Address 0xFEC0_0000 contains 0x8000_00A8 (MSB to LSB) Register at 0xA8 contains 0xFFDD_FFFF (AB to A8) Example: Map A configuration sequence, 4-byte data write to register at address offset 0xA8. Initial values:r0 contains ...

Page 134

Configuration Register Access in Big-Endian Mode When the processor and the Tsi107 are in big-endian mode, software must either use the load/store with byte reversed instructions (lhbrx, lwbrx, sthbrx, and stwbrx) or byte-swap the CONFIG_ADDR and CONFIG_DATA values before ...

Page 135

Code sequence: stwbrx r0,0,r1 sync sthbrx r2,0,r3 sync Results:Address 0x8000_0CF8 contains 0x8000_0004 (MSB to LSB) Register at 0xA8 contains 0xFFFF_CCDD (AB to A8) Example: Map A configuration sequence, 4-byte data write to register at address offset 0xA8, using byte-swapped values ...

Page 136

Table 4-2. Tsi107 Processor-Accessible Configuration Registers<Emphasis> (Continued) Address Register Offset 0x09 Standard programming interface 0x0A Subclass code 0x0B Base Class code 0x0C Cache line size 0x0D Latency timer 0x0E Header type 0x0F BIST control 0x10 Local memory base address register ...

Page 137

Table 4-2. Tsi107 Processor-Accessible Configuration Registers<Emphasis> (Continued) Address Register Offset 0x90, Memory ending address registers 0x94 0x98, Extended memory ending address 0x9C registers 0xA0 Memory bank enable register 0xA3 Page mode counter/timer 0xA8 Processor interface configuration 1 0xAC Processor interface ...

Page 138

Figure 4-1 shows the processor accessible configuration space. Reserved Device ID (0x0004) PCI Status Base Class Code BIST Control Peripheral Control and Status Registers Base Address Register MAX LAT PCI Arbiter Control Output Driver Control Embedded Utilities Memory Block Base ...

Page 139

PCI-Accessible Configuration Registers Table 4-3 lists the subset of configuration registers that are accessible from the PCI bus. Note that configuration addresses not defined in Table 4-3 are reserved. Table 4-3. Tsi107 Configuration Registers Accessible from the PCI Bus ...

Page 140

Figure 4-2 shows the PCI accessible configuration space. Reserved Device ID (0x0004) PCI Status Base Class Code BIST Control Peripheral Control and Status Registers Base Address Register MAX LAT PCI Arbiter Control Figure 4-2. PCI Accessible Configuration Space 4.2 PCI ...

Page 141

Table 4-4. PCI Configuration Space Header Summary<Emphasis> (Continued) Address Register Name Offset 0x0E Header type 0x0F BIST control 0x10 Local Memory Base Address Register 0x14 Peripheral Control and Status Registers Base Address Register 0x18–0x2 — F 0x30 Expansion ROM base ...

Page 142

PCI Command Register—Offset 0x04 The 2-byte PCI command register, shown in Figure 4-3, provides control over the ability to generate and respond to PCI cycles. Table 4-5 describes the bits of the PCI command register. Memory-write-and-invalidate Parity error response ...

Page 143

Table 4-5. Bit Settings for PCI Command Register—0x04<Emphasis> (Continued) Reset Bits Name Value 2 Bus master 1 (host) 0 (agent) 1 Memory space 0 I/O space 4.2.2 PCI Status Register—Offset 0x06 The 2-byte PCI status register, shown in Figure 4-4, ...

Page 144

Table 4-6. Bit Settings for PCI Status Register—0x06 Reset Bits Name Value 15 Detected parity error 14 Signaled system error 13 Received master-abort 12 Received target-abort 11 Signaled target-abort 10–9 DEVSEL timing 8 Data parity detected 7 Fast back-to-back capable ...

Page 145

PCI Base Class Code—Offset 0x0B Table 4-8 describes the PCI base class code register (PBCCR). Bits Reset Value msb 7–0 Mode- 0x06 When Tsi107 is configured as a host bridge to indicate “Host Bridge.” dependent 0x0E When Tsi107 is ...

Page 146

Tsi107. Table 4-11 describes the bits of the LMBAR. Table 4-11. Local Memory Base Address Register Bit Definitions—0x10 Reset Bits Name Value 31–12 Inbound 0x0000_0 ...

Page 147

PCI Arbiter Control Register (PACR)—Offset 0x46 This register controls the on-chip arbitration for external PCI masters. As many as five external devices are supported. Table 4-14. PCI Arbiter Control Register Bit Definitions—0x46 Reset Bits R/W Value msb 15 x ...

Page 148

Peripheral Logic Power Management Configuration Registers (PMCRs) The power management configuration registers (PMCRs) control the power management functions of the peripheral logic. For more information on the power management feature of both the processor core and the peripheral logic, ...

Page 149

Table 4-15. Bit Settings for Power Management Configuration Register 1—0x70<Emphasis> Reset Bits Name Value BR1_WAKE 0 5 DOZE 0 4 NAP 0 3 SLEEP 0 2–1 CKO_MODE 00 0 — 0 IDT Description Power management enable ...

Page 150

Power Management Configuration Register 2 (PMCR2)—Offset 0x72 Power management configuration register 2 (PMCR2), shown in Figure 4- 1-byte register located at offset 0x72. PCI_HOLD_DELAY[0–2] DLL_STANDARD Figure 4-6. Power Management Configuration Register 2 (PMCR2)—0x72 Table 4-16 describes the ...

Page 151

Table 4-16. Power Management Configuration Register 2—0x72<Emphasis> (Continued) Reset Bits Name Value 2 PLL_SLEEP 0 1 — — 0 4.4 Output/Clock Driver and Miscellaneous I/O Control Registers Output driver control allows for impedance matching of electrical signals. When ...

Page 152

Table 4-17 describes the bits of ODCR. . Table 4-17. Output Driver Control Register Bit Definitions—0x73 Bits Name Value msb 7 DRV_PCI addr<73> 6 DRV_CPU 5 DRV_MEM_CTRL_1 4 DRV_MEM_CTRL_2 3 DRV_PCI_CLK_1 2 DRV_PCI_CLK_2 22 Reset x Driver capability for PCI ...

Page 153

Table 4-17. Output Driver Control Register Bit Definitions—0x73<Emphasis> (Continued) Bits Name 1 DRV_MEM_CLK_1 0 DRV_MEM_CLK_2 4.4.2 CLK Driver Control Register—0x74 Figure 4-8 describes the output enable/disable capability available for the clock signals through the clock driver control register (CDCR). DRV_CPU_CLK_2 ...

Page 154

Table 4-18. CLK Driver Control Register Bit Definitions—0x74<Emphasis> (Continued) Bit Name 13 PCI_CLK1_DIS 12 PCI_CLK2 _DIS 11 PCI_CLK3_DIS 10 PCI_CLK4_DIS 9 DRV_CPU_CLK_1 8 DRV_CPU_CLK_2 7 SDRAM_SYNC_OUT addr<74> 6 SDRAM_CLK0_DIS 5 SDRAM_CLK1_DIS 4 SDRAM_CLK2_DIS 3 SDRAM_CLK3_DIS 2 CPU_CLK0_DIS 1 CPU_CLK1_DIS 0 ...

Page 155

Miscellaneous I/O Control Register—0x76 Figure 4-9 describes the miscellaneous I/O control register (MIOCR) that controls the type of output for the MCP, SRESET and QACK signals. NO_HI-Z_QACK SRESET_OD_MODE MCP_OD_MODE Figure 4-9. Miscellaneous I/O Control Register—0x76 Table 4-19 describes the ...

Page 156

Embedded Utilities Memory Block Base Address Register—0x78 The embedded utilities memory block base address register (EUMBBAR), shown in Table 4-20, controls the placement of the embedded utilities memory block (EUMB). See Section 3.4, “Embedded Utilities Memory Block (EUMB).” Table ...

Page 157

Starting Address Bank Figure 4-10. Memory Starting Address Register 1—0x80 Starting Address Bank Figure 4-11. Memory Starting Address Register 2—0x84 Table 4-21. Bit Settings for Memory Starting Address Registers ...

Page 158

Extended Starting Address 6 Extended Starting Address Figure 4-13. Extended Memory Starting Address Register 2—0x8C Table 4-22. Bit Settings for Extended Memory Starting Address Registers 1 and 2 ...

Page 159

Ending Address Bank Figure 4-15. Memory Ending Address Register 2—0x94 Table 4-23. Bit Settings for Memory Ending Address Registers 1 and 2 Bits Name 31–24 Ending address bank 3 23–16 Ending address bank 2 15–8 Ending ...

Page 160

Table 4-24. Bit Settings for Extended Memory Ending Address Registers 1 and 2 Bits Name 31–26 — 25–24 Extended ending address 3 23–18 — 17–16 Extended ending address 2 15–10 — 9–8 Extended ending address 1 7–2 — 1–0 Extended ...

Page 161

Table 4-25. Bit Settings for Memory Bank Enable Register—0xA0 Bits 4.6.3 Memory Page Mode Register—0xA3 The 1-byte memory page mode register, shown in Figure 4-19 and Table 4-26, contains the PGMAX parameter ...

Page 162

Table 4-26. Bit Settings for Memory Page Mode Register—0xA3 Reset Bits Name Value 7–0 PGMAX All 0s For DRAM/EDO configurations, the value of PGMAX multiplied by 64 determines the maximum RAS assertion interval for retained page mode. When programmed to ...

Page 163

Table 4-27 describes the PICR1 bit settings. Table 4-27. Bit Settings for PICR1—0xA8 Bits Name 31–24 — addr<ab> 23–22 CF_BREAD_WS addr<aa> 21 — 20 RCS0 19 — 18–17 PROC_TYPE 16 ADDRESS_MAP 15–14 CF_MP_ID addr <a9> IDT Reset Value All 1s ...

Page 164

Table 4-27. Bit Settings for PICR1—0xA8 <Emphasis> (Continued) Bits Name 13 CF_LBA_EN 12 FLASH_WR_EN 11 MCP_EN 10 TEA_EN 9–8 — 7 NO_BUS_ addr<a8> WIDTH_CHECK 6 ST_GATH_EN 5 LE_MODE 34 Reset Value See Local bus slave access enable. Note 0 Local ...

Page 165

Table 4-27. Bit Settings for PICR1—0xA8 <Emphasis> (Continued) Bits Name 4 CF_LOOP_SNOOP 3 CF_APARK 2 Speculative PCI Reads 1–0 CF_MP 4.7.2 Processor Interface Configuration Register 2—0xAC Figure 4-21 shows the bits of the PICR2. SERIALIZE_ON_CFG ...

Page 166

Table 4-28 describes the bit settings for PICR2. Table 4-28. Bit Settings for PICR2—0xAC Bits Name 31–30 — 29 SERIALIZE_ON_CFG 28 — 27 NO_SNOOP_EN 26 CF_FF0_LOCAL 25 FLASH_WR_LOCKOUT 24–20 — 19–18 CF_SNOOP_WS 17–11 — 36 Reset Value 00 Reserved 0 ...

Page 167

Table 4-28. Bit Settings for PICR2—0xAC <Emphasis> (Continued) Bits Name 10–9 CF_LBCLAIM_WS 8–4 — 3–2 CF_APHASE_WS 1–0 — 4.8 Error Handling Registers Chapter 13, “Error Handling,” describes specific error conditions and how the Tsi107 responds to them. The registers at ...

Page 168

Table 4-29 describes the bits of the ECC single-bit error counter. Table 4-29. Bit Settings for ECC Single-Bit Error Counter Register—0xB8 Reset Bits Name Value 7–0 ECC single-bit error All 0s counter 4.8.1.2 ECC Single-Bit Error Trigger Register—0xB9 The ECC ...

Page 169

Error Enabling and Detection Registers The error detection registers are bit-reset type registers. That is, reading from these registers occurs normally; however, write operations are different in that bits (error flags) can be cleared but not set. A bit ...

Page 170

Table 4-31 describes the enable bits for ErrEnR1. Table 4-31. Bit Settings for Error Enabling Register 1 (ErrEnR1)—0xC0 Reset Bits Name Value 7 RX_SERR_EN 0 6 PCI target PERR enable 0 5 Memory select error 0 enable 4 Memory refresh ...

Page 171

Figure 4-25 shows the enable bits for ErrEnR2. PCI SERR Enable PCI Address Parity Error Enable Figure 4-25. Error Enabling Register 2 (ErrEnR2)—0xC4 Table 4-32 describes the enable bits for ErrEnR2. Table 4-32. Bit Settings for Error Enabling Register 2 ...

Page 172

Error Detection Registers 1 and 2—0xC1 and 0xC5 The error detection registers 1 and 2 (ErrDR1 and ErrDR2), shown in Figure 4-26 and Figure 4-27, contain error flags that report when the Tsi107 detects a specific error condition. Figure ...

Page 173

Table 4-33. Bit Settings for Error Detection Register 1 (ErrDR1)—0xC1 <Emphasis> (Con- Reset Bits Name Value 2 Memory read parity 0 error/ECC single-bit error trigger exceeded 1–0 Unsupported processor 00 transaction Figure 4-27 shows the bits for error detection register ...

Page 174

Table 4-34. Bit Settings for Error Detection Register 2 (ErrDR2)—0xC5 <Emphasis> (Con- Reset Bits Name Value 2 Processor memory write parity error 1 — 0 Flash ROM write error 4.8.2.3 Processor Bus Error Status Register—0xC3 The processor bus error status ...

Page 175

PCI Bus Error Status Register—0xC7 The PCI bus error status register latches the state of the PCI C/BE[3:0] signals when an error is detected on the PCI bus as defined in Section 13.3.3, “PCI Interface Errors.” Figure 4-29 shows ...

Page 176

Table 4-37 describes the bits of the processor/PCI error address register. Table 4-37. Bit Settings for Processor/PCI Error Address Register—0xC8 Reset Bits Name Value 31–24 Error address 0x00 A[24:31] or AD[7:0]—Dependent on whether the error is a processor bus error ...

Page 177

Table 4-38. Bit Settings for the AMBOR—0xE0 <Emphasis> (Continued) Bits Name 5–4 — 3 PCI_COMPATIBILITY_ HOLE 2 PROC_COMPATIBILITY_ HOLE 1–0 — 4.10 Memory Control Configuration Registers The four 32-bit memory control configuration registers (MCCRs) set all RAM and ROM parameters. ...

Page 178

Memory Control Configuration Register 1—0xF0 Figure 4-32 and Table 4-39 show the memory control configuration register 1 (MCCR1) format and bit settings. PCKEN RAM_TYPE SREN MEMGO BURST DBUS_SIZ[0–1] ROMNAL ROMFAL Figure 4-32. Memory Control Configuration Register ...

Page 179

Table 4-39. Bit Settings for MCCR1—0xF0<Emphasis> (Continued) Reset Bits Name Value 22–21 DBUS_SIZ[0– BURST 0 19 MEMGO 0 18 SREN 0 17 RAM_TYPE 1 16 PCKEN 0 IDT Description Read-only. This field indicates the state of the memory ...

Page 180

Table 4-39. Bit Settings for MCCR1—0xF0<Emphasis> (Continued) Reset Bits Name Value 15–14 Bank 7 row 00 13–12 Bank 6 row 00 11–10 Bank 5 row 00 9–8 Bank 4 row 00 7–6 Bank 3 row 00 5–4 Bank 2 row ...

Page 181

Memory Control Configuration Register 2—0xF4 Figure 4-33 and Table 4-40 show the memory control configuration register 2 (MCCR2) format and bit settings. EDO ECC_EN INLINE_RD_EN INLINE_WR_EN INLINE_PAR_NOT_ECC ASFALL[0–3] ASRISE[0–3] TS_WAIT_TIMER[0– Figure 4-33. Memory ...

Page 182

Table 4-40. Bit Settings for MCCR2—0xF4 Reset Bits Name Value 31–29 TS_WAIT_ 000 Transaction start wait states timer. The minimum time allowed for ROM/Flash/Port X TIMER[0–2] devices to enter high impedance is 2 memory system clocks. TS_WAIT_TIMER[0–2] adds wait states ...

Page 183

Table 4-40. Bit Settings for MCCR2—0xF4<Emphasis> (Continued) Reset Bits Name Value 20 INLINE_PAR_ 0 In-line parity —not ECC. This bit selects between the ECC and parity checking/correction NOT_ECC mechanisms of the in-line data path when performing memory reads. This bit ...

Page 184

Table 4-40. Bit Settings for MCCR2—0xF4<Emphasis> (Continued) Reset Bits Name Value 1 RSV_PG 0 Reserve page register. If this bit is set, the Tsi107 reserves one of the four page registers at all times. This is equivalent to only allowing ...

Page 185

Memory Control Configuration Register 3—0xF8 Figure 4-34 and Table 4-41 show memory control configuration register 3 (MCCR3) format and bit settings. BSTOPRE[2–5] REFREC Figure 4-34. Memory Control Configuration Register 3 (MCCR3)—0xF8 Table 4-41. Bit ...

Page 186

Table 4-41. Bit Settings for MCCR3—0xF8 <Emphasis> (Continued) Reset Bits Name Value 19 CPX 0 18–15 RAS 0000 6P 14–12 CAS 000 5 11–9 CP 000 4 56 Description CAS write timing modifier. For DRAM/EDO only. When set, this bit ...

Page 187

Table 4-41. Bit Settings for MCCR3—0xF8 <Emphasis> (Continued) Reset Bits Name Value 8–6 CAS 000 3 5–3 RCD 000 2 2–0 RP 000 1 IDT Description CAS assertion interval for the first access. For DRAM/EDO only. These bits control the ...

Page 188

Memory Control Configuration Register 4—0xFC Figure 4-35 and Table 4-42 show memory control configuration register 4 (MCCR4) format and bit settings. EXTROM BUF_TYPE[0] WMODE PRETOACT ACTOPRE ...

Page 189

Table 4-42. Bit Settings for MCCR4—0xFC<Emphasis> (Continued) Reset Bits Name Value 22 BUF_TYPE[ EXTROM 0 20 BUF_TYPE[1] 1 19–18 BSTOPRE[0– DBUS_SIZE[ — REGDIMM 0 IDT Description Most significant bit of the memory ...

Page 190

Table 4-42. Bit Settings for MCCR4—0xFC<Emphasis> (Continued) Reset Bits Name Value 14–8 SDMODE All 0s SDRAM mode register. For SDRAM only. These bits specify the SDRAM mode register data to be written to the SDRAM array during power-up configuration. Note ...

Page 191

Chapter 5 Processor Bus Interface The Tsi107 provides flexible support for system designs using the PowerPC 603e, PowerPC 740/750, and MPC7400 microprocessors via the processor (60x) bus interface. The Tsi107’s 60x bus interface provides a 32-bit address bus and a ...

Page 192

Tsi107 ADDRESS ARBITRATION ADDRESS START ADDRESS BUS TRANSFER TSIZ[0:2], TBST, ATTRIBUTE ADDRESS TERMINATION DATA ARBITRATION DH[0:31], DL[0:31] DATA TRANSFER DATA TERMINATION INTERRUPT/RESET LOCAL BUS LBCLAIM, DBGLB SLAVE CONTROLS Notes: 1. 603e/750 processors do not have a SHD signal. – All ...

Page 193

ADDRESS ARBITRATION ADDRESS START ADDRESS BUS TRANSFER TSIZ[0:2], TBST, ATTRIBUTE ADDRESS TERMINATION DATA ARBITRATION DH[0:31], DL[0:31] DATA TRANSFER DATA TERMINATION INTERRUPT/RESET MP CONTROLS LOCAL BUS SLAVE LBCLAIM, DBGLB CONTROLS Note: 1. 603e/750 processors do not have a SHD signal. – ...

Page 194

AACK and ARTRY signals are sampled. See Section 5.1.3, “Processor Bus Interface Configuration Registers,” for more ...

Page 195

ADDRESS TENURE ARBITRATION TRANSFER INDEPENDENT ADDRESS AND DATA Figure 5-3. Overlapping Tenures on the 60x Bus for a Single-Beat Transfer The basic functions of the address and data tenures are as follows: • Address tenure — Arbitration: During arbitration, address ...

Page 196

The following signals are used for address bus arbitration: • BR0 and BR1 (bus request)—Assertion indicates that a bus master is requesting mastership of the address bus. • BG0 and BG1 (bus grant)—Assertion indicates that a bus master may, with ...

Page 197

Address Arbitration Overview The Tsi107 provides arbitration for the processor address bus. The external input signals to the arbiter are BR0 in a single processor configuration, and BR0 and BR1 in a dual-processor configuration. In addition to the external ...

Page 198

TS) without first having asserted address bus request. During the same clock cycle, the Tsi107’s internal bus request is asserted to request access to the 60x bus, thereby causing the negation of BG0. Following the address tenure of processor 0, ...

Page 199

Bus Clock TS 60x Address AACK DBGn TA 60x Data 5.3.3 Address Transfer Attribute Signals During the address transfer phase of an address tenure, the address of the bus operation to be performed is placed on address signals (A[0:31]) ...

Page 200

Table 5-1. Tsi107 Responses to 60x Transfer Type Signals TT[0:4] Bus Operation 01010 Read 01110 Read-with-intent-to-modify 11010 Read atomic 11110 Read-with-intent-to- modify-atomic 00010 Write-with-flush 00110 Write-with-kill 10010 Write-with-flush-atomic 01000 sync 10000 eieio 01100 Kill 01101 icbi 01011 Read-with-no-intent-to-cache (RWNITC) 00000 ...