PSD913F1-B-90JI ST Microelectronics, PSD913F1-B-90JI Datasheet - Page 12

PSD913F1-B-90JI

Manufacturer Part Number

PSD913F1-B-90JI

Description

Flash In-System Programmable ISP Peripherals For 8-bit MCUs

Manufacturer

ST Microelectronics

Datasheet

1.PSD913F1-B-90JI.pdf

(94 pages)

- Current page: 12 of 94

- Download datasheet (477Kb)

PSD9XX

Architectural

Overview

(cont.)

8

PSD9XX Family

5.7 In-System Programming

Using the JTAG signals on Port C, the entire PSD9XX device can be programmed or

erased without the use of the microcontroller (ISP). The main Flash memory can also be

programmed in-system by the microcontroller executing the programming algorithms out of

the Secondary Flash memory, or SRAM (IAP). The Secondary Flash memory can be

programmed the same way by executing out of the main Flash memory. The PLD logic

or other PSD9XX configuration can be programmed through the JTAG port or a device

programmer. Table 4 indicates which programming methods can program different

functional blocks of the PSD9XX.

5.8 Power Management Unit

The Power Management Unit (PMU) in the PSD9XX gives the user control of the power

consumption on selected functional blocks based on system requirements. The PMU

includes an Automatic Power Down unit (APD) that will turn off device functions due to

microcontroller inactivity. The APD unit has a Power Down Mode that helps reduce power

consumption.

The PSD9XX also has some bits that are configured at run-time by the MCU to reduce

power consumption of the PLD. The turbo bit in the PMMR0 register can be turned off and

the PLD will latch its outputs and go to sleep until the next transition on its inputs.

Additionally, bits in the PMMR2 register can be set by the MCU to block signals from

entering the PLD to reduce power consumption. See section 9.5.

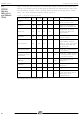

Table 4. Methods of Programming Different Functional Blocks of the PSD9XX

Main Flash Memory

Secondary Flash Memory

PLD Array (DPLD and GPLD)

PSD Configuration

Functional Block

JTAG-ISP

Yes

Yes

Yes

Yes

Programmer

Device

Yes

Yes

Yes

Yes

Preliminary Information

IAP

Yes

Yes

No

No

Related parts for PSD913F1-B-90JI

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

120V - 100W DMOS AUDIO AMPLIFIER WITH MUTE/ST-BY

Manufacturer:

ST Microelectronics

Datasheet:

Part Number:

Description:

Manufacturer:

ST Microelectronics

Datasheet:

Part Number:

Description:

N-channel 55V - 0.07 Ohm - 22A StripFET Power MOSFET

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

Old PRODUCT: Not Suitable For Design-in

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

Programmable poly-phase energy calculator IC

Manufacturer:

ST Microelectronics

Datasheet:

Part Number:

Description:

High-voltage, High Current Switch

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

Single Chip Read & Write Channel

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

10A Triacs

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

20A Triacs

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

-

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

ac Line Switch

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

Video And Audio Signals Switchings For The Peri-television Plug

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

H/v Deflection With Automatic VCR Switching

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

Switch Mode Power Supply Controller

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

Stepper Motor Driver

Manufacturer:

ST Microelectronics, Inc.

Datasheet: