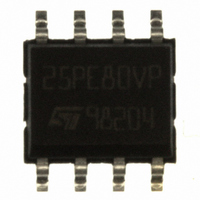

M25PE80-VMN6TP NUMONYX, M25PE80-VMN6TP Datasheet - Page 45

M25PE80-VMN6TP

Manufacturer Part Number

M25PE80-VMN6TP

Description

IC FLASH 8MBIT 75MHZ 8SOIC

Manufacturer

NUMONYX

Series

Forté™r

Datasheet

1.M25PE80-VMN6TP.pdf

(66 pages)

Specifications of M25PE80-VMN6TP

Format - Memory

FLASH

Memory Type

FLASH

Memory Size

8M (1M x 8)

Speed

75MHz

Interface

SPI, 3-Wire Serial

Voltage - Supply

2.7 V ~ 3.6 V

Operating Temperature

-40°C ~ 85°C

Package / Case

8-SOIC (3.9mm Width)

Package

8SOIC N

Cell Type

NOR

Density

8 Mb

Architecture

Sectored

Block Organization

Symmetrical

Typical Operating Supply Voltage

3.3 V

Sector Size

256Byte x 4096

Timing Type

Synchronous

Interface Type

Serial-SPI

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

M25PE80-VMN6TPTR

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

M25PE80-VMN6TP

Manufacturer:

ST

Quantity:

6 000

Part Number:

M25PE80-VMN6TP

Manufacturer:

ST

Quantity:

20 000

M25PE80

6.17

Release from deep power-down (RDP)

Once the device has entered the deep power-down mode, all instructions are ignored

except the release from deep power-down (RDP) instruction. Executing this instruction

takes the device out of the deep power-down mode.

The release from deep power-down (RDP) instruction is entered by driving Chip Select (S)

Low, followed by the instruction code on serial data input (D). Chip Select (S) must be driven

Low for the entire duration of the sequence.

The instruction sequence is shown in

The release from deep power-down (RDP) instruction is terminated by driving Chip Select

(S) High. Sending additional clock cycles on Serial Clock (C), while Chip Select (S) is driven

Low, cause the instruction to be rejected, and not executed.

After Chip Select (S) has been driven High, followed by a delay, t

standby mode. Chip Select (S) must remain High at least until this period is over. The device

waits to be selected, so that it can receive, decode and execute instructions.

Any release from deep power-down (RDP) instruction, while an erase, program or write

cycle is in progress, is rejected without having any effects on the cycle that is in progress.

Figure 23. Release from deep power-down (RDP) instruction sequence

S

C

D

Q

High Impedance

0

1

2

Instruction

3

4

5

6

Figure

7

23.

Deep power-down mode

t

RDP

RDP

, the device is put in the

Standby mode

Instructions

AI06807

45/66