ISL62871HRUZ-T Intersil, ISL62871HRUZ-T Datasheet - Page 16

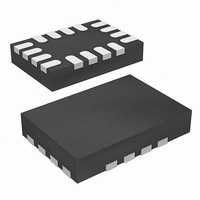

ISL62871HRUZ-T

Manufacturer Part Number

ISL62871HRUZ-T

Description

IC CTRLR DC/DC PWM 16-TQFN

Manufacturer

Intersil

Datasheet

1.ISL62871HRUZ-T.pdf

(25 pages)

Specifications of ISL62871HRUZ-T

Pwm Type

Controller

Number Of Outputs

1

Frequency - Max

330kHz

Duty Cycle

100%

Voltage - Supply

3.3 V ~ 25 V

Buck

Yes

Boost

No

Flyback

No

Inverting

No

Doubler

No

Divider

No

Cuk

No

Isolated

No

Operating Temperature

-10°C ~ 100°C

Package / Case

16-UTQFN (16-µTQFN)

Frequency-max

330kHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

ISL62871HRUZ-T

Manufacturer:

INTERSIL

Quantity:

20 000

makes this an unattractive option for all but the lowest

current applications. Efficiency is dramatically improved

when the free-wheeling diode is replaced with a MOSFET

that is turned on whenever the high-side MOSFET is turned

off. This modification to the standard DC/DC buck regulator

is referred to as synchronous rectification, the topology

implemented by the ISL62871 and ISL62872 controllers.

Diode Emulation

The polarity of the output inductor current is defined as

positive when conducting away from the phase node, and

defined as negative when conducting towards the phase

node. The DC component of the inductor current is positive,

but the AC component known as the ripple current, can be

either positive or negative. Should the sum of the AC and

DC components of the inductor current remain positive for

the entire switching period, the converter is in

continuous-conduction-mode (CCM.) However, if the

inductor current becomes negative or zero, the converter is

in discontinuous-conduction-mode (DCM.)

Unlike the standard DC/DC buck regulator, the synchronous

rectifier can sink current from the output filter inductor during

DCM, reducing the light-load efficiency with unnecessary

conduction loss as the low-side MOSFET sinks the inductor

current. The ISL62871 and ISL62872 controllers avoid the

DCM conduction loss by making the low-side MOSFET

emulate the current-blocking behavior of a diode. This

smart-diode operation called diode-emulation-mode (DEM)

is triggered when the negative inductor current produces a

positive voltage drop across the r

MOSFET for eight consecutive PWM cycles while the

LGATE pin is high. The converter will exit DEM on the next

PWM pulse after detecting a negative voltage across the

r

It is characteristic of the R

switching frequency to decrease while in DCM, increasing

efficiency by reducing unnecessary gate-driver switching

losses. The extent of the frequency reduction is proportional

to the reduction of load current. Upon entering DEM, the

PWM frequency is forced to fall approximately 30% by

forcing a similar increase of the window voltage V

measure is taken to prevent oscillating between modes at

the boundary between CCM and DCM. The 30% increase of

V

frequency to jump back to the nominal CCM value.

Power-On Reset

The IC is disabled until the voltage at the VCC pin has

increased above the rising power-on reset (POR) threshold

voltage V

when the voltage

POR threshold voltage V

noise filter of approximately 1µs.

DS(ON)

W

is removed upon exit of DEM, forcing the PWM switching

of the low-side MOSFET.

VCC_THR

at the

. The controller will become disabled

VCC pin decreases below the falling

VCC_THF

3

architecture for the PWM

16

DS(ON)

. The POR detector has a

of the low-side

W

ISL62871, ISL62872

. This

V

Prior to pulling EN above the V

voltage, the following criteria must be met:

Start-Up Timing

Once VCC has ramped above V

be enabled by pulling the EN pin voltage above the

input-high threshold V

voltage at the SREF pin begins slewing to the designated

VID set-point. The converter output voltage at the FB

feedback pin follows the voltage at the SREF pin. During

soft-start, The regulator always operates in CCM until the

soft-start sequence is complete.

PGOOD Monitor

The PGOOD pin indicates when the converter is capable of

supplying regulated voltage. The PGOOD pin is an

undefined impedance if the VCC pin has not reached the

rising POR threshold V

the falling POR threshold V

pull-down resistance corresponds to a specific protective

fault, thereby reducing troubleshooting time and effort.

Table 3 maps the pull-down resistance of the PGOOD pin to

the corresponding fault status of the controller.

LGATE and UGATE MOSFET Gate-Drivers

The LGATE pin and UGATE pins are MOSFET driver

outputs. The LGATE pin drives the low-side MOSFET of the

converter while the UGATE pin drives the high-side

MOSFET of the converter.

The LGATE driver is optimized for low duty-cycle

applications where the low-side MOSFET experiences long

conduction times. In this environment, the low-side

MOSFETs require exceptionally low r

have large parasitic charges that conduct transient currents

within the devices in response to high dv/dt switching

present at the phase node. The drain-gate charge in

particular can conduct sufficient current through the driver

pull-down resistance that the V

exceeded and turned on. For this reason the LGATE driver

has been designed with low pull-down resistance and high

sink current capability to ensure clamping the MOSFETs

gate voltage below V

IN

- V

- V

Soft-Start or Undervoltage

and PVCC Voltage Sequence

reset voltage V

application

PVCC

VIN

VCC Below POR

TABLE 3. PGOOD PULL-DOWN RESISTANCE

CONDITION

Overvoltage

Overcurrent

must be 3.3V or the minimum required by the

is at least equivalent to the VCC rising power-on

VCC_THR

GS(th)

ENTHR

VCC_THR

.

VCC_THF

. Approximately 20µs later, the

GS(th)

ENTHR

VCC_THR

, or if

PGOOD RESISTANCE

. The PGOOD

DS(ON)

of the device can be

the

rising threshold

Undefined

, the controller can

VCC pin is below

95Ω

65Ω

35Ω

and tend to

August 14, 2008

FN6707.0