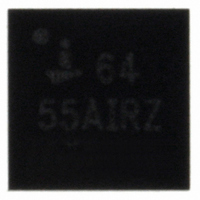

ISL6455AIRZ-TK Intersil, ISL6455AIRZ-TK Datasheet - Page 8

ISL6455AIRZ-TK

Manufacturer Part Number

ISL6455AIRZ-TK

Description

IC REG TRPL SYNCH DUAL LDO 24QFN

Manufacturer

Intersil

Datasheet

1.ISL6455IRZ-TK.pdf

(12 pages)

Specifications of ISL6455AIRZ-TK

Applications

Converter, FPGAs

Voltage - Input

4.2 ~ 5.5 V

Number Of Outputs

3

Voltage - Output

0.8 ~ 3.3 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

24-VQFN Exposed Pad, 24-HVQFN, 24-SQFN, 24-DHVQFN

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

ISL6455AIRZ-TKTR

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ISL6455AIRZ-TK

Manufacturer:

Intersil

Quantity:

2 100

Pin Descriptions

PVCC - Positive supply for the power (internal FET) stage of

the PWM section.

SGND - Analog ground for the PWM. All internal control

circuits are referenced to this pin.

EN - The PWM controller is enabled when this pin is HIGH,

and disabled when the pin is pulled LOW. It is a CMOS logic-

level input (referenced to V

V

EN_LDO - LDO1 and LDO2 are enabled when this pin is

HIGH, and disabled when the pin is pulled LOW. It is a

CMOS logic-level input (referenced to V

CT - Timing capacitor pin to set the 25ms minimum pulse

width for the RESET signal.

RESET - This pin is the output of the reset supervisory

circuit, which monitors VIN_PWM. The IC asserts a RESET

signal whenever the supply voltage drops below a preset

threshold. It is kept asserted for a minimum of 25ms after

V

push-pull. The device will continue to operate until V

below the UVLO threshold.

When EN = LOW then RESET = HIGH and the moment EN

is made HIGH the RESET will pulse LOW for a period of

25ms minimum (VIN > Reset threshold). If VIN < reset

threshold then it will switch low and stay low for a period of

25ms after VIN_PWM crosses the reset threshold.

PG_LDO - This is a high impedance open drain output that

provides the status of both LDOs. When either of the outputs

are out of regulation, PG_LDO goes LOW.

CC1 - This is the compensation capacitor connection for

LDO1. Connect a 0.033µF capacitor from CC1 to

GND_LDO.

CC2 - This is the compensation capacitor connection for

LDO2. Connect a 0.033µF capacitor from CC2 to

GND_LDO.

V

minimum 2.2µF, low ESR capacitor to GND_LDO for stable

operation.

GND_LDO - Ground pin for LDO1 and LDO2.

V

minimum 2.2µF, low ESR capacitor to GND_LDO for stable

operation.

PGND - Power ground for the PWM controller stage.

V

converter for the purpose of detecting the over and

undervoltage conditions.

IN

CC

OUT2

OUT1

OUT

_LDO - This is the input voltage pin for LDO1 and LDO2.

(V

- This I/O pin senses the output voltage of the PWM

IN

- This pin is the output of LDO2. Bypass with a

- This pin is the output of LDO1. Bypass with a

) has risen above the reset threshold. The output is

IN

).

8

IN

).

ISL6455, ISL6455A

IN

drops

PG_PWM - This pin is an active pull-up/pull-down able to

source/sink 1mA (min.) at 0.4V from V

is HIGH when V

FB_LDO1 and FB_LDO2 - These pins are used to set the

LDO output with the proper selection of resistors. i.e. Ra and

Rb for LDO1 and Rc and Rd for LDO2. Resistors should be

chosen to provide a minimum current of 200µA load for each

LDO output.

LX - The LX pin is the switching node of synchronous buck

converter, connected internally at the junction point of the

upper MOSFET source and lower MOSFET drain. Connect

this pin to the output inductor.

V

stage and must be closely decoupled to ground.

SYNC - This is the external clock synchronization input. The

device can be synchronized to 500kHz to 1MHz switching

frequency. If unused then it should be tied to GND or VCC

GND - Tie this pin to the ground plane with a low impedance,

shortest possible path.

FB_PWM- This is used to set the value of the output voltage

of the PWM with external resistors Re and Rf.

Functional Description

The ISL6455 is a 3-in-1 multi-output regulator designed for

FPGA and wireless chipset power applications. The device

integrates a single synchronous buck regulator with dual

LDOs. The PWM output can be set by choosing appropriate

values for Re and Rf. At a setting of 1.8V the synchronous

buck regulator provides for an efficiency greater than 92%.

The LDO1 can be set with resistor pair Rc and Rd. The

LDO2 can be set with the resistor pair Ra and Rb.

Undervoltage lock-out (UVLO) prevents the converter from

turning on when the input voltage is less than 2.6V typical.

Additional blocks include output overcurrent protection,

thermal sensor, PGOOD detectors, RESET function and

shutdown logic.

Synchronous Buck Regulator

The synchronous buck regulator with integrated N- and

P-channel power MOSFETs and external voltage setting

resistors provides for adjustable voltages from the PWM.

Synchronous rectification with internal MOSFETs is used to

achieve higher efficiency and reduced number of external

components. Operating frequency is typically 750kHz

allowing the use of smaller inductor and capacitor values.

The device can be synchronized to an external clock signal

in the range of 500kHz to 1MHz. The PG_PWM output

indicates loss of regulation on PWM output.

The PWM architecture uses a peak current mode control

scheme with internal slope compensation. At the beginning

of each clock cycle, the high side P-channel MOSFET is

turned on. The current in the inductor ramps up and is

IN

- This pin is the power supply for the PWM controller

OUT

is within ±8% (typical).

IN

/SGND. This output

December 21, 2005

FN9196.0