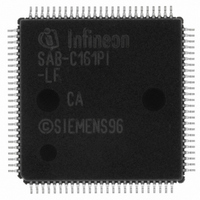

SAB-C161PI-LF CA Infineon Technologies, SAB-C161PI-LF CA Datasheet - Page 20

SAB-C161PI-LF CA

Manufacturer Part Number

SAB-C161PI-LF CA

Description

IC MICROCONTROLLER 16BIT 100TQFP

Manufacturer

Infineon Technologies

Series

C16xxr

Datasheet

1.SAF-C161PI-LM_CA.pdf

(82 pages)

Specifications of SAB-C161PI-LF CA

Core Processor

C166

Core Size

16-Bit

Speed

20MHz

Connectivity

EBI/EMI, I²C, SPI, UART/USART

Peripherals

POR, PWM, WDT

Number Of I /o

76

Program Memory Type

ROMless

Ram Size

3K x 8

Voltage - Supply (vcc/vdd)

4.5 V ~ 5.5 V

Data Converters

A/D 4x10b

Oscillator Type

Internal

Operating Temperature

0°C ~ 70°C

Package / Case

100-LFQFP

Packages

PG-TQFP-100

Max Clock Frequency

20.0 MHz

Sram (incl. Cache)

3.0 KByte

A / D Input Lines (incl. Fadc)

4

Program Memory

0.0 KByte

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Other names

B161PILFCAXT

SAB-C161PI-LF CA

SAB-C161PI-LFCAINTR

SABC161PILFCAXT

SP000014344

SAB-C161PI-LF CA

SAB-C161PI-LFCAINTR

SABC161PILFCAXT

SP000014344

Data Sheet

Interrupt System

With an interrupt response time within a range from just 5 to 12 CPU clocks (in case of

internal program execution), the C161PI is capable of reacting very fast to the

occurrence of non-deterministic events.

The architecture of the C161PI supports several mechanisms for fast and flexible

response to service requests that can be generated from various sources internal or

external to the microcontroller. Any of these interrupt requests can be programmed to

being serviced by the Interrupt Controller or by the Peripheral Event Controller (PEC).

In contrast to a standard interrupt service where the current program execution is

suspended and a branch to the interrupt vector table is performed, just one cycle is

‘stolen’ from the current CPU activity to perform a PEC service. A PEC service implies a

single byte or word data transfer between any two memory locations with an additional

increment of either the PEC source or the destination pointer. An individual PEC transfer

counter is implicity decremented for each PEC service except when performing in the

continuous transfer mode. When this counter reaches zero, a standard interrupt is

performed to the corresponding source related vector location. PEC services are very

well suited, for example, for supporting the transmission or reception of blocks of data.

The C161PI has 8 PEC channels each of which offers such fast interrupt-driven data

transfer capabilities.

A separate control register which contains an interrupt request flag, an interrupt enable

flag and an interrupt priority bitfield exists for each of the possible interrupt sources. Via

its related register, each source can be programmed to one of sixteen interrupt priority

levels. Once having been accepted by the CPU, an interrupt service can only be

interrupted by a higher prioritized service request. For the standard interrupt processing,

each of the possible interrupt sources has a dedicated vector location.

Fast external interrupt inputs are provided to service external interrupts with high

precision requirements. These fast interrupt inputs feature programmable edge

detection (rising edge, falling edge or both edges).

Software interrupts are supported by means of the ‘TRAP’ instruction in combination with

an individual trap (interrupt) number.

The following table shows all of the possible C161PI interrupt sources and the

corresponding hardware-related interrupt flags, vectors, vector locations and trap

(interrupt) numbers.

Note: Interrupt nodes which are not used by associated peripherals, may be used to

generate software controlled interrupt requests by setting the respective interrupt

request bit (xIR).

18

&3,

1999-07