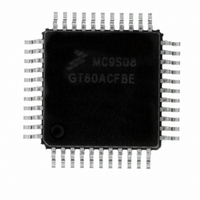

MC9S08GT60ACFBE Freescale Semiconductor, MC9S08GT60ACFBE Datasheet - Page 73

MC9S08GT60ACFBE

Manufacturer Part Number

MC9S08GT60ACFBE

Description

IC MCU 60K FLASH 4K RAM 44-QFP

Manufacturer

Freescale Semiconductor

Series

HCS08r

Datasheet

1.MC9S08GT60ACFDER.pdf

(302 pages)

Specifications of MC9S08GT60ACFBE

Core Processor

HCS08

Core Size

8-Bit

Speed

40MHz

Connectivity

I²C, SCI, SPI

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

36

Program Memory Size

60KB (60K x 8)

Program Memory Type

FLASH

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 3.6 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

44-QFP

Cpu Family

HCS08

Device Core Size

8b

Frequency (max)

40MHz

Interface Type

I2C/SCI/SPI

Total Internal Ram Size

4KB

# I/os (max)

36

Number Of Timers - General Purpose

4

Operating Supply Voltage (typ)

2.5/3.3V

Operating Supply Voltage (max)

3.6V

Operating Supply Voltage (min)

1.8/2.08V

On-chip Adc

8-chx10-bit

Instruction Set Architecture

CISC

Operating Temp Range

-40C to 85C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

44

Package Type

PQFP

Processor Series

S08GT

Core

HCS08

Data Bus Width

8 bit

Data Ram Size

4 KB

Maximum Clock Frequency

20 MHz

Number Of Programmable I/os

39

Number Of Timers

2

Operating Supply Voltage

0 V to 1.8 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

EWS08

Development Tools By Supplier

M68EVB908GB60E, M68DEMO908GB60E

Minimum Operating Temperature

- 40 C

For Use With

M68DEMO908GB60E - BOARD DEMO MC9S08GB60M68EVB908GB60E - BOARD EVAL FOR MC9S08GB60

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC9S08GT60ACFBE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Part Number:

MC9S08GT60ACFBE

Manufacturer:

FREESCALE深圳进口

Quantity:

20 000

Company:

Part Number:

MC9S08GT60ACFBER

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

5.8.1

This direct page register includes two unimplemented bits which always read 0, four read/write bits, one

read-only status bit, and one write-only bit. These bits are used to configure the IRQ function, report status,

and acknowledge IRQ events.

Freescale Semiconductor

IRQMOD

IRQEDG

IRQACK

Reset

IRQPE

IRQIE

Field

IRQF

5

4

3

2

1

0

W

R

Interrupt Pin Request Status and Control Register (IRQSC)

Interrupt Request (IRQ) Edge Select — This read/write control bit is used to select the polarity of edges or

levels on the IRQ pin that cause IRQF to be set. The IRQMOD control bit determines whether the IRQ pin is

sensitive to both edges and levels or only edges. When the IRQ pin is enabled as the IRQ input and is configured

to detect rising edges, the optional pullup resistor is re-configured as an optional pulldown resistor.

0 IRQ is falling edge or falling edge/low-level sensitive.

1 IRQ is rising edge or rising edge/high-level sensitive.

IRQ Pin Enable — This read/write control bit enables the IRQ pin function. When this bit is set, the IRQ pin can

be used as an interrupt request. Also, when this bit is set, either an internal pull-up or an internal pull-down

resistor is enabled depending on the state of the IRQMOD bit.

0 IRQ pin function is disabled.

1 IRQ pin function is enabled.

IRQ Flag — This read-only status bit indicates when an interrupt request event has occurred.

0 No IRQ request.

1 IRQ event detected.

IRQ Acknowledge — This write-only bit is used to acknowledge interrupt request events (write 1 to clear IRQF).

Writing 0 has no meaning or effect. Reads always return 0. If edge-and-level detection is selected (IRQMOD = 1),

IRQF cannot be cleared while the IRQ pin remains at its asserted level.

IRQ Interrupt Enable — This read/write control bit determines whether IRQ events generate a hardware

interrupt request.

0 Hardware interrupt requests from IRQF disabled (use polling).

1 Hardware interrupt requested whenever IRQF = 1.

IRQ Detection Mode — This read/write control bit selects either edge-only detection or edge-and-level

detection. The IRQEDG control bit determines the polarity of edges and levels that are detected as interrupt

request events. See

0 IRQ event on falling edges or rising edges only.

1 IRQ event on falling edges and low levels or on rising edges and high levels.

0

0

7

Figure 5-2. Interrupt Request Status and Control Register (IRQSC)

= Unimplemented or Reserved

0

0

6

Section 5.5.2.2, “Edge and Level

IRQEDG

Table 5-2. IRQSC Field Descriptions

MC9S08GB60A Data Sheet, Rev. 2

0

5

IRQPE

0

4

Description

Sensitivity”

IRQF

Chapter 5 Resets, Interrupts, and System Configuration

3

0

for more details.

IRQACK

0

0

2

IRQIE

0

1

IRQMOD

0

0

73