MCP6V01T-E/MNY Microchip Technology, MCP6V01T-E/MNY Datasheet - Page 6

MCP6V01T-E/MNY

Manufacturer Part Number

MCP6V01T-E/MNY

Description

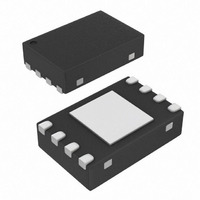

IC OPAMP AUTO-ZERO SGL 8-TDFN

Manufacturer

Microchip Technology

Datasheet

1.MCP6V01RD-TCPL.pdf

(44 pages)

Specifications of MCP6V01T-E/MNY

Slew Rate

0.5 V/µs

Package / Case

8-TDFN

Amplifier Type

Chopper (Zero-Drift)

Number Of Circuits

1

Output Type

Rail-to-Rail

Gain Bandwidth Product

1.3MHz

Current - Input Bias

1pA

Voltage - Input Offset

2µV

Current - Supply

300µA

Current - Output / Channel

22mA

Voltage - Supply, Single/dual (±)

1.8 V ~ 5.5 V

Operating Temperature

-40°C ~ 125°C

Mounting Type

Surface Mount

Number Of Channels

1

Common Mode Rejection Ratio (min)

130 dB

Input Offset Voltage

0.002 mV

Input Bias Current (max)

1 pA

Operating Supply Voltage

3 V, 5 V

Maximum Operating Temperature

+ 125 C

Minimum Operating Temperature

- 40 C

Mounting Style

SMD/SMT

Shutdown

No

Supply Voltage (max)

5.5 V

Supply Voltage (min)

1.8 V

Technology

CMOS

Voltage Gain Db

156 dB

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

MCP6V01DM-VOS - DEMO BOARD FOR MCP6V01MCP6V01RD-TCPL - REF DESIGN THERMCPL FOR MCP6V01

-3db Bandwidth

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

MCP6V01T-E/MNYTR

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MCP6V01T-E/MNY

Manufacturer:

Renesas

Quantity:

91

Part Number:

MCP6V01T-E/MNY

Manufacturer:

MICROCHIP/微芯

Quantity:

20 000

MCP6V01/2/3

1.3

FIGURE 1-1:

FIGURE 1-2:

Time.

FIGURE 1-3:

FIGURE 1-4:

DS22058C-page 6

V

V

OUT

V

V

V

I

CS

I

I

V

OUT

DD

SS

CS

V

OS

DD

OS

IN

IN

1 µA

(typical)

-2 µA

(typical)

V

(typical)

Timing Diagrams

V

0V

DD

DD

High-Z

/5 MΩ

t

t

ODR

ON

1.8V

t

V

t

STL

STR

IL

Amplifier Start Up.

Offset Correction Settling

Output Overdrive Recovery.

Chip Select (MCP6V03).

V

DD

(typical)

(typical)

(typical)

300 µA

300 µA

/2

5 pA

V

SS

V

t

ODR

IH

1.8V to 5.5V

V

V

V

V

OS

OS

OS

OS

t

OFF

V

+ 50 µV

– 50 µV

+ 50 µV

+ 50 µV

DD

(typical)

(typical)

(typical)

High-Z

/5 MΩ

-2 µA

1 µA

1.4

The circuits used for the DC and AC tests are shown in

Figure 1-5

out as discussed in Section 4.3.8 “Supply Bypassing

and Filtering”. R

of R

FIGURE 1-5:

Most Non-Inverting Gain Conditions.

FIGURE 1-6:

Most Inverting Gain Conditions.

The circuit in

dynamic behavior (i.e., IMD, t

potentiometer balances the resistor network (V

should equal V

mode input voltage is V

input (V

10 V/V.

FIGURE 1-7:

Input Behavior.

V

V

V

V

V

DD

DD

IN

F

IN

IN

MCP6V0X

MCP6V0X

and R

/3

/3

20.0 kΩ

20.0 kΩ

ERR

0.1%

0.1%

Test Circuits

R

R

R

R

N

G

N

G

and

G

) appears at V

to minimize bias current effects.

Figure

Figure 1-7

REF

20.0 kΩ

MCP6V0X

20.0 kΩ

N

0.1%

0.1%

V

V

V

DD

DD

DD

is equal to the parallel combination

at DC). The op amp’s common

AC and DC Test Circuit for

AC and DC Test Circuit for

Test Circuit for Dynamic

100 nF

100 nF

100 nF

1-6. Lay the bypass capacitors

1 µF

© 2008 Microchip Technology Inc.

CM

R

R

25 turn

24.9 Ω

1 µF

1 µF

50Ω

F

F

tests the op amp input’s

OUT

= V

STR

IN

R

R

with a noise gain of

, t

/2. The error at the

ISO

ISO

R

STL

C

C

ISO

L

L

C

and t

L

V

REF

R

R

L

L

ODR

V

V

V

L

L

L

V

V

V

R

). The

OUT

OUT

OUT

L

OUT