MCF53014CMJ240J Freescale Semiconductor, MCF53014CMJ240J Datasheet - Page 27

MCF53014CMJ240J

Manufacturer Part Number

MCF53014CMJ240J

Description

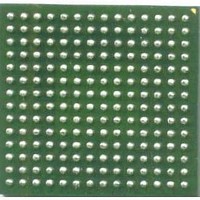

IC MCU 32BIT 128KB 256MAPBGA

Manufacturer

Freescale Semiconductor

Series

MCF5301xr

Datasheet

1.MCF53010CQT240.pdf

(62 pages)

Specifications of MCF53014CMJ240J

Core Processor

Coldfire V3

Core Size

32-Bit

Speed

240MHz

Connectivity

EBI/EMI, Ethernet, I²C, MMC, SPI, SSI, UART/USART, USB, USB OTG

Peripherals

DMA, PWM, WDT

Number Of I /o

83

Program Memory Size

16KB (16K x 8)

Program Memory Type

Cache

Ram Size

128K x 8

Voltage - Supply (vcc/vdd)

1.08 V ~ 3.6 V

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

256-LBGA

Processor Series

MCF5301x

Core

ColdFire V3

Data Bus Width

32 bit

Data Ram Size

16 bit

Interface Type

I2C, UART, DSPI

Maximum Clock Frequency

400 KHz, 20 MHz, 25 MHz

Number Of Timers

4

Operating Supply Voltage

- 0.5 V to + 2 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

JLINK-CF-BDM26, EWCF

Development Tools By Supplier

M53015EVB, M53017KIT, M53017MOD

Minimum Operating Temperature

- 40 C

On-chip Adc

13 bit

On-chip Dac

16 bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Data Converters

-

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MCF53014CMJ240J

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

5.7

The SDRAM controller supports accesses to main SDRAM memory from any internal master. It supports either standard

SDRAM or double data rate (DDR) SDRAM, but it does not support both at the same time.

5.7.1

The following timing numbers indicate when data will be latched or driven onto the external bus, relative to the memory bus

clock, when operating in SDR mode on write cycles and relative to SD_DQS on read cycles. The device’s SDRAM controller

is a DDR controller that has an SDR mode. Because it is designed to support DDR, a DQS pulse must still be supplied to the

device for each data beat of an SDR read. The processor accomplishes this by asserting a signal named SD_SDR_DQS during

Freescale Semiconductor

SDRAM Bus

SDR SDRAM AC Timing Characteristics

FB_CSn, FB_BE/BWEn

FB_CSn, FB_OE,

FB_BE/BWEn

FB_D[31:X]

FB_D[31:X]

FB_A[23:0]

FB_A[23:0]

Preliminary—Subject to Change Without Notice

FB_CLK

FB_R/W

FB_CLK

FB_R/W

FB_OE

FB_TS

FB_TS

FB_TA

FB_TA

Figure 11. FlexBus Read Timing

Figure 12. Flexbus Write Timing

MCF5301x Data Sheet, Rev. 5

FB1

FB1

ADDR[31:X]

ADDR[31:X]

S0

S0

FB2

FB2

FB6

FB6

ADDR[23:0]

ADDR[23:0]

S1

S1

DATA

DATA

FB4

S2

S2

FB7

FB7

FB5

Preliminary Electrical Characteristics

S3

S3

FB3

FB3

27