AGLN010V2-UCG36 Actel, AGLN010V2-UCG36 Datasheet - Page 101

AGLN010V2-UCG36

Manufacturer Part Number

AGLN010V2-UCG36

Description

FPGA - Field Programmable Gate Array 10K System Gates IGLOO nano

Manufacturer

Actel

Datasheet

1.AGLN030V5-ZUCG81.pdf

(140 pages)

Specifications of AGLN010V2-UCG36

Processor Series

AGLN010

Core

IP Core

Number Of Macrocells

86

Maximum Operating Frequency

250 MHz

Number Of Programmable I/os

23

Supply Voltage (max)

1.5 V

Supply Current

3 uA

Maximum Operating Temperature

+ 70 C

Minimum Operating Temperature

- 20 C

Development Tools By Supplier

AGLN-Nano-Kit, AGLN-Z-Nano-Kit, AGL-Dev-Kit-SCS, Silicon-Explorer II, Silicon-Sculptor 3, SI-EX-TCA, FLASHPRO 4, FlashPro 3, FLASHPRO LITE

Mounting Style

SMD/SMT

Supply Voltage (min)

1.2 V

Number Of Gates

10 K

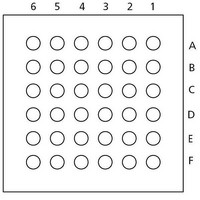

Package / Case

uCSP-36

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 101 of 140

- Download datasheet (5Mb)

JTAG 1532 Characteristics

Table 2-111 • JTAG 1532

Table 2-112 • JTAG 1532

Parameter

t

t

t

t

t

t

F

t

t

t

Note:

Parameter

t

t

t

t

t

t

F

t

t

t

Note:

DISU

DIHD

TMSSU

TMDHD

TCK2Q

RSTB2Q

TRSTREM

TRSTREC

TRSTMPW

DISU

DIHD

TMSSU

TMDHD

TCK2Q

RSTB2Q

TRSTREM

TRSTREC

TRSTMPW

TCKMAX

TCKMAX

For specific junction temperature and voltage supply levels, refer to

For specific junction temperature and voltage supply levels, refer to

JTAG timing delays do not include JTAG I/Os. To obtain complete JTAG timing, add I/O buffer delays to

the corresponding standard selected; refer to the I/O timing characteristics in the

Characteristics" section on page 2-15

Timing Characteristics

1.5 V DC Core Voltage

1.2 V DC Core Voltage

Commercial-Case Conditions: T

Commercial-Case Conditions: T

Test Data Input Setup Time

Test Data Input Hold Time

Test Mode Select Setup Time

Test Mode Select Hold Time

Clock to Q (data out)

Reset to Q (data out)

TCK Maximum Frequency

ResetB Removal Time

ResetB Recovery Time

ResetB Minimum Pulse

Test Data Input Setup Time

Test Data Input Hold Time

Test Mode Select Setup Time

Test Mode Select Hold Time

Clock to Q (data out)

Reset to Q (data out)

TCK Maximum Frequency

ResetB Removal Time

ResetB Recovery Time

ResetB Minimum Pulse

J

J

= 70°C, Worst-Case VCC = 1.425 V

= 70°C, Worst-Case VCC = 1.14 V

for more details.

Description

Description

R ev i si o n 1 1

Table 2-6 on page 2-6

Table 2-6 on page 2-6

IGLOO nano Low Power Flash FPGAs

25.00

TBD

1.00

2.00

1.00

2.00

8.00

0.58

0.00

Std.

11.00

30.00

15

TBD

Std.

1.50

3.00

1.50

3.00

9.00

1.18

0.00

for derating values.

for derating values.

"User I/O

Units

MHz

Units

MHz

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

2- 87

Related parts for AGLN010V2-UCG36

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

AGLN010V2-QNG48I

Manufacturer:

Actel

Datasheet:

Part Number:

Description:

AGLN010V2-UCG36I

Manufacturer:

Actel

Datasheet:

Part Number:

Description:

FPGA - Field Programmable Gate Array 10K System Gates IGLOO nano

Manufacturer:

Actel

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Silicon Sculptor Programming Mod

Manufacturer:

Actel

Part Number:

Description:

MCU, MPU & DSP Development Tools InSystem Programming ProASICPLUS Devices

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators PQ160 Module

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators Axcelerator Adap Module Kit

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators Evaluation

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators AFDX Solutions

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators SILICON SCULPTOR ADAPTER MODULE

Manufacturer:

Actel

Datasheet:

Part Number:

Description:

Programming Socket Adapters & Emulators Axcelerator Adap Module Kit

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators Evaluation

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators Silicon Sculptor Software

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators InSystem Programming ProASICPLUS Devices

Manufacturer:

Actel

Part Number:

Description:

Programming Socket Adapters & Emulators Evaluation

Manufacturer:

Actel