MC33696MOD434EV Freescale Semiconductor, MC33696MOD434EV Datasheet - Page 63

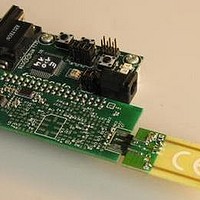

MC33696MOD434EV

Manufacturer Part Number

MC33696MOD434EV

Description

MCU, MPU & DSP Development Tools MC33696 (ECHO) RF C EVAL

Manufacturer

Freescale Semiconductor

Specifications of MC33696MOD434EV

Processor To Be Evaluated

MC9S08RG60

Interface Type

RS-232

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 63 of 80

- Download datasheet (2Mb)

21.9 Digital Interface Timing

NOTES:

1

2

Freescale Semiconductor

Operating supply voltage and temperature range see

schematic (see

measurement at V

9.10 Data setup time

9.2 SCLK period

9.8 Configuration enable time

9.3 Enable lead time

9.4 Enable lag time

9.5 Sequential transfer delay

9.6 Data hold time

9.7 Data setup time

9.9

See

The digital interface can be used in SPI burst protocol, i.e., with a continuous clock on SCLK port. For example, one (or more)

read access followed by one (or more) write access and so on. In this case and for a practical use, the pulse required on

CONFB between accesses must be higher than 100 ns only if STROBE signal is always set to high level.

Section 9.1, “Clock

Figure 47

CC

Parameter

= 3.0 V, T

to

Generator” for T

Figure 54

A

= 25°C.

through

Receive mode, DME = 1,

from SCLK to MOSI

Configuration mode,

from SCLK to MISO

Configuration mode, from

SCLK to MOSI

Configuration mode, from

SCLK to MOSI

Crystal oscillator is running.

digclk

Figure

MC33696 Data Sheet, Rev. 12

values.

Test Conditions

Comments

Table

54), unless otherwise specified. Typical values reflect average

3. Values refer to the circuit recommended in the application

3 x T

3 x T

Min

100

100

120

100

20

—

1

digclk

digclk

1

1

Limits

Typ

—

—

—

—

—

—

—

—

—

Electrical Characteristics

Max

100

—

—

—

—

—

—

—

—

2

Unit

μs

μs

μs

ns

ns

μs

ns

ns

ns

63

Related parts for MC33696MOD434EV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: