CY7C1371D-133BGC Cypress Semiconductor Corp, CY7C1371D-133BGC Datasheet - Page 12

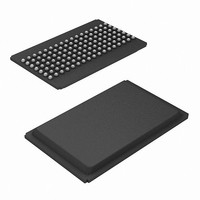

CY7C1371D-133BGC

Manufacturer Part Number

CY7C1371D-133BGC

Description

IC,SYNC SRAM,512KX36,CMOS,BGA,119PIN,PLASTIC

Manufacturer

Cypress Semiconductor Corp

Datasheet

1.CY7C1373D-100AXC.pdf

(33 pages)

Specifications of CY7C1371D-133BGC

Format - Memory

RAM

Memory Type

SRAM - Synchronous

Memory Size

18M (512K x 36)

Speed

133MHz

Interface

Parallel

Voltage - Supply

3.135 V ~ 3.6 V

Operating Temperature

0°C ~ 70°C

Package / Case

119-BGA

Lead Free Status / RoHS Status

Contains lead / RoHS compliant by exemption

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY7C1371D-133BGC

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Company:

Part Number:

CY7C1371D-133BGCT

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Truth Table

Partial Truth Table for Read/Write

Partial Truth Table for Read/Write

Notes

Document Number: 38-05556 Rev. *I

Deselect cycle

Deselect cycle

Deselect cycle

Continue deselect cycle

Read cycle (begin burst)

Read cycle (continue burst)

NOP/dummy read (begin burst)

Dummy read (continue burst)

Write cycle (begin burst)

Write cycle (continue burst)

NOP/write abort (begin burst)

Write abort (continue burst)

Ignore clock edge (stall)

Sleep mode

Function (CY7C1371D)

Read

Write no bytes written

Write byte A – (DQ

Write byte B – (DQ

Write byte C – (DQ

Write byte D – (DQ

Write all Bytes

Function (CY7C1373D)

Read

Write - no bytes written

Write byte A – (DQ

Write byte B – (DQ

Write all bytes

2. X = “Don't Care.” H = Logic HIGH, L = Logic LOW. BW

3. Write is defined by BW

4. When a write cycle is detected, all IOs are tri-stated, even during byte writes.

5. The DQs and DQP

6. CEN = H, inserts wait states.

7. Device powers up deselected and the IOs in a tri-state condition, regardless of OE.

8. OE is asynchronous and is not sampled with the clock rise. It is masked internally during write cycles. During a read cycle DQs and DQP

9. Table only lists a partial listing of the byte write combinations. Any Combination of BW

selects are asserted, see truth table for details.

is inactive or when the device is deselected, and DQs and DQP

Operation

[2, 3, 4, 5, 6, 7, 8]

X

B

C

D

B

pins are controlled by the current cycle and the OE signal. OE is asynchronous and is not sampled with the clock.

A

A

X

and DQP

and DQP

and DQP

and DQP

and DQP

and DQP

, and WE. See truth table for read/write.

B

D

A

C

A

B

)

)

)

)

)

)

Address

External

External

External

Current

Used

None

None

None

None

None

None

Next

Next

Next

Next

X

CE

= 0 signifies at least one byte write select is active, BW

[2, 3, 9]

[2, 3, 9]

H

X

X

X

X

X

X

X

X

X

L

L

L

L

1

CE

X

WE

H

H

H

H

X

X

X

X

X

X

X

X

X

L

= data when OE is active.

H

L

L

L

L

L

L

2

CE

H

X

X

X

X

L

X

L

X

X

X

X

L

L

3

ZZ

H

L

L

L

L

L

L

L

L

L

L

L

L

L

BW

X

X

H

H

H

H

L

L

ADV/LD WE BW

is valid Appropriate write is based on which byte write is active.

A

H

H

H

H

H

X

X

L

L

L

L

L

L

L

H

H

X

X

X

X

X

X

L

X

X

X

X

L

BW

WE

X

H

H

H

H

H

L

L

L

L

L

L

B

X

X

X

X

X

X

X

X

H

H

X

X

L

L

X

= valid signifies that the desired byte write

X

OE

X

X

X

X

H

H

X

X

X

X

X

X

L

L

BW

BW

CEN CLK

X

H

H

H

H

X

H

H

L

L

L

L

H

L

L

L

X

L

L

L

L

L

L

L

L

L

C

A

L->H

L->H Data out (Q)

L->H

L->H Data in (D)

L->H Data in (D)

L->H

L->H

L->H

L->H Data out (Q)

L->H

L->H

L->H

L->H

X

X

= tri-state when OE

CY7C1371D

CY7C1373D

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

Tri-state

BW

BW

Page 12 of 33

H

H

H

H

H

H

X

L

X

L

DQ

L

L

–

D

B

[+] Feedback