CY8C3245LTI-163 Cypress Semiconductor Corp, CY8C3245LTI-163 Datasheet - Page 10

CY8C3245LTI-163

Manufacturer Part Number

CY8C3245LTI-163

Description

CY8C3245LTI-163

Manufacturer

Cypress Semiconductor Corp

Series

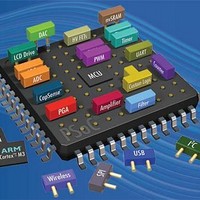

PSOC™ 3 CY8C32xxr

Specifications of CY8C3245LTI-163

Core Processor

8051

Core Size

8-Bit

Speed

50MHz

Connectivity

EBI/EMI, I²C, LIN, SPI, UART/USART

Peripherals

CapSense, DMA, POR, PWM, WDT

Number Of I /o

38

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Eeprom Size

1K x 8

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Data Converters

A/D 2x12b, D/A 1x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

*

Processor Series

CY8C32

Core

8051

Data Bus Width

32 bit

Data Ram Size

4 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

50 MHz

Number Of Programmable I/os

46

Number Of Timers

4

Operating Supply Voltage

1.71 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

38

Eeprom Memory Size

1KB

Ram Memory Size

4KB

Cpu Speed

50MHz

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

3. Pin Descriptions

IDAC0

Low resistance output pin for high current DAC (IDAC).

Extref0, Extref1

External reference input to the analog system.

GPIO

General purpose I/O pin provides interfaces to the CPU, digital

peripherals, analog peripherals, interrupts, LCD segment drive,

and CapSense.

I2C0: SCL, I2C1: SCL

I

Any I/O pin can be used for I

required.

I2C0: SDA, I2C1: SDA

I

Any I/O pin can be used for I

required.

Ind

Inductor connection to boost pump.

kHz XTAL: Xo, kHz XTAL: Xi

32.768-kHz crystal oscillator pin.

MHz XTAL: Xo, MHz XTAL: Xi

4- to 25- MHz crystal oscillator pin.

Document Number: 001-56955 Rev. *J

2

2

C SCL line providing wake from sleep on an address match.

C SDA line providing wake from sleep on an address match.

Figure 2-6. Example PCB Layout for 100-pin TQFP Part for Optimal Analog Performance

2

2

C SCL if wake from sleep is not

C SDA if wake from sleep is not

Plane

Vssd

Vddd

Vssd

nTRST

Optional JTAG test reset programming and debug port

connection to reset the JTAG connection.

SIO

Special I/O provides interfaces to the CPU, digital peripherals

and interrupts with a programmable high threshold voltage,

analog comparator, high sink current, and high impedance state

when the device is unpowered.

SWDCK

Serial wire debug clock programming and debug port

connection.

SWDIO

Serial wire debug input and output programming and debug port

connection.

SWV.

Single wire viewer debug output.

TCK

JTAG test clock programming and debug port connection.

TDI

JTAG test data in programming and debug port connection.

TDO

JTAG test data out programming and debug port connection.

TMS

JTAG test mode select programming and debug port connection.

Vssa

Vdda

PSoC

Plane

Vssa

®

3: CY8C32 Family

Data Sheet

Page 10 of 119

[+] Feedback