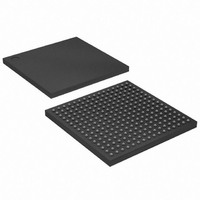

XC3S200-4FTG256C Xilinx Inc, XC3S200-4FTG256C Datasheet - Page 115

XC3S200-4FTG256C

Manufacturer Part Number

XC3S200-4FTG256C

Description

FPGA Spartan®-3 Family 200K Gates 4320 Cells 630MHz 90nm Technology 1.2V 256-Pin FTBGA

Manufacturer

Xilinx Inc

Series

Spartan™-3r

Datasheet

1.XC3S50-4VQG100C.pdf

(217 pages)

Specifications of XC3S200-4FTG256C

Package

256FTBGA

Family Name

Spartan®-3

Device Logic Units

4320

Device System Gates

200000

Maximum Internal Frequency

630 MHz

Typical Operating Supply Voltage

1.2 V

Maximum Number Of User I/os

173

Ram Bits

221184

Number Of Logic Elements/cells

4320

Number Of Labs/clbs

480

Total Ram Bits

221184

Number Of I /o

173

Number Of Gates

200000

Voltage - Supply

1.14 V ~ 1.26 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

256-LBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

122-1338

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

XC3S200-4FTG256C

Manufacturer:

XILINX/赛灵思

Quantity:

20 000

Table 78: Pin Behavior After Power-Up, During Configuration (Continued)

DS099-4 (v2.5) December 4, 2009

Product Specification

IO_Lxxy_#/

D5

IO_Lxxy_#/

D6

IO_Lxxy_#/

D7

IO_Lxxy_#/

CS_B

IO_Lxxy_#/

RDWR_B

IO_Lxxy_#/

BUSY/DOUT

DUAL: Dual-purpose configuration pins (INIT_B has a pull-up resistor to VCCO_4 or VCCO_BOTTOM always active

during configuration, regardless of HSWAP_EN pin)

IO_Lxxy_#/

INIT_B

DCI: Digitally Controlled Impedance reference resistor input pins

IO_Lxxy_#/

VRN_#

IO/VRN_#

IO_Lxxy_#/

VRP_#

IO/VRP_#

GCLK: Global clock buffer inputs

IO_Lxxy_#/

GCLK0 through

GCLK7

VREF: I/O bank input reference voltage pins

IO_Lxxy_#/

VREF_#

IO/VREF_#

CONFIG: Dedicated configuration pins (pull-up resistor to VCCAUX always active during configuration, regardless of

HSWAP_EN pin)

CCLK

PROG_B

DONE

M2

Pin Name

R

INIT_B (I/OD)

DONE (I/OD)

PROG_B (I)

CCLK (I/O)

DOUT (O)

M2=0 (I)

(pull-up)

<0:0:0>

Master

Serial Modes

INIT_B (I/OD)

DONE (I/OD)

PROG_B (I)

Configuration Mode Settings <M2:M1:M0>

DOUT (O)

CCLK (I)

(pull-up)

M2=1 (I)

<1:1:1>

Slave

www.xilinx.com

INIT_B (I/OD)

DONE (I/OD)

RDWR_B (I)

PROG_B (I)

CCLK (I/O)

SelectMap Parallel Modes

BUSY (O)

CS_B (I)

(pull-up)

M2=0 (I)

D5 (I/O)

D6 (I/O)

D7 (I/O)

<0:1:1>

Master

INIT_B (I/OD)

DONE (I/OD)

RDWR_B (I)

PROG_B (I)

BUSY (O)

CS_B (I)

CCLK (I)

(pull-up)

M2=1 (I)

D5 (I/O)

D6 (I/O)

D7 (I/O)

<1:1:0>

Spartan-3 FPGA Family: Pinout Descriptions

Slave

Via JPROG_B

DONE (I/OD)

PROG_B (I),

JTAG Mode

instruction

M2=1 (I)

<1:0:1>

Configuration

ConfigRate

UnusedPin

UnusedPin

UnusedPin

UnusedPin

UnusedPin

UnusedPin

UnusedPin

UnusedPin

UnusedPin

UnusedPin

UnusedPin

UnusedPin

UnusedPin

UnusedPin

Bitstream

DriveDone

DonePipe

DonePin

ProgPin

CclkPin

Option

Persist

Persist

Persist

Persist

Persist

Persist

M2Pin

115