CY8C3866AXI-040 Cypress Semiconductor Corp, CY8C3866AXI-040 Datasheet - Page 22

CY8C3866AXI-040

Manufacturer Part Number

CY8C3866AXI-040

Description

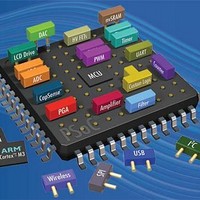

PSOC 3 TQFP

Manufacturer

Cypress Semiconductor Corp

Series

PSOC™ 3 CY8C38xxr

Datasheet

1.CY8C3865LTI-058.pdf

(129 pages)

Specifications of CY8C3866AXI-040

Package / Case

*

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Speed

67MHz

Number Of I /o

62

Eeprom Size

2K x 8

Core Processor

8051

Program Memory Type

FLASH

Ram Size

8K x 8

Program Memory Size

64KB (64K x 8)

Data Converters

A/D 2x20b, D/A 4x8b

Oscillator Type

Internal

Peripherals

CapSense, DMA, LCD, POR, PWM, WDT

Connectivity

CAN, EBI/EMI, I²C, LIN, SPI, UART/USART, USB

Core Size

8-Bit

Processor Series

CY8C38

Core

8051

Data Bus Width

32 bit

Data Ram Size

8 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

67 MHz

Number Of Programmable I/os

28 to 72

Number Of Timers

4

Operating Supply Voltage

0.5 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

62

Eeprom Memory Size

2KB

Ram Memory Size

8KB

Cpu Speed

67MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor

Quantity:

135

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

NXP

Quantity:

112

Company:

Part Number:

CY8C3866AXI-040

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Part Number:

CY8C3866AXI-040

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

Company:

Part Number:

CY8C3866AXI-040ES2

Manufacturer:

CYPRESS

Quantity:

153

5.5 Nonvolatile Latches (NVLs)

PSoC has a 4-byte array of nonvolatile latches (NVLs) that are used to configure the device at reset. The NVL register map is shown

in

Table 5-2. Device Configuration NVL Register Map

The details for individual fields and their factory default settings are shown in

Table 5-3. Fields and Factory Default Settings

Although PSoC Creator provides support for modifying the device configuration NVLs, the number of NVL erase / write cycles is limited

– see

Document Number: 001-11729 Rev. *R

PRTxRDM[1:0]

XRESMEN

CFGSPEED

DPS{1:0]

ECCEN

DIG_PHS_DLY[3:0]

Table

Register Address

“Nonvolatile Latches (NVL))”

5-2.

Field

0x00

0x01

0x02

0x03

Controls reset drive mode of the corresponding IO port.

See

are set to the same mode.

Controls whether pin P1[2] is used as a GPIO or as an

external reset. See

description.

Controls the speed of the IMO-based clock during the

device boot process, for faster boot or low-power

operation

Controls the usage of various P1 pins as a debug port.

See

page 61.

Controls whether ECC flash is used for ECC or for general

configuration and data storage. See

Memory”

Selects the digital clock phase delay.

XRESMEN

“Reset Configuration”

“Programming, Debug Interfaces, Resources”

PRT12RDM[1:0]

PRT3RDM[1:0]

7

on page 21.

on page 104.

DIG_PHS_DLY[3:0]

“Pin Descriptions”

6

Description

on page 39. All pins of the port

PRT2RDM[1:0]

PRT6RDM[1:0]

5

“Flash Program

on page 10, XRES

4

on

Table

ECCEN

PRT1RDM[1:0]

PRT5RDM[1:0]

3

00b (default) - high impedance analog

01b - high impedance digital

10b - resistive pull up

11b - resistive pull down

0 (default for 68-pin and 100-pin parts) - GPIO

1 (default for 48-pin parts) - external reset

0 (default) - 12 MHz IMO

1 - 48 MHz IMO

00b - 5-wire JTAG

01b (default) - 4-wire JTAG

10b - SWD

11b - debug ports disabled

0 (default) - ECC disabled

1 - ECC enabled

See the TRM for details.

5-3:.

PSoC

2

DPS[1:0]

®

3: CY8C38 Family

Settings

1

PRT15RDM[1:0]

PRT0RDM[1:0]

PRT4RDM[1:0]

Data Sheet

Page 22 of 129

CFGSPEED

0

[+] Feedback