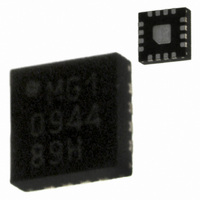

PIC16F526-I/MG Microchip Technology, PIC16F526-I/MG Datasheet

PIC16F526-I/MG

Specifications of PIC16F526-I/MG

Available stocks

Related parts for PIC16F526-I/MG

PIC16F526-I/MG Summary of contents

Page 1

... Legend Input Output Power Note 1: In the PIC16F526, the programming high voltage is internally generated. To activate the Program/Verify mode, high voltage of I IHH © 2007 Microchip Technology Inc. PIC16F526 1.1 Hardware Requirements The PIC16F526 requires one power supply for V (5.0V) and one for V 1 ...

Page 2

... PIC16F526 2.0 MEMORY MAPPING The Program Memory map of the PIC16F526 device is shown in Figure 2-1. In Program/Verify mode, the Program Memory extends from 0x000 to 0x7FF. FIGURE 2-1: MEMORY MAP On-chip User Program Memory (Page 0) On-chip User Program Memory (Page 1) Reset Vector Flash Data Memory ...

Page 3

... Because this is a 12-bit core, the two MSbs of the data word are ignored. The commands that are available are described in Table 3-1. Mapping Hex (MSb ... LSb) Value start_bit, data (14), stop_bit 4 start_bit, data (14), stop_bit PIC16F526 Data DS41317B-page 3 ...

Page 4

... PIC16F526 3.1.2.1 Load Data After receiving this command, the device will clock in 14 bits as a “data word” when 16 cycles are applied, as described previously. Because this is a 12-bit core, the FIGURE 3-2: LOAD DATA COMMAND (PROGRAM/VERIFY RB1 (ICSPCLK) RB0 (ICSPDAT) T SET T 3 ...

Page 5

... T 1 SET HLD 100 ns min. the appropriate memory (User Program Memory, Flash Data Memory or Test Program Memory) will begin after this command is received and decoded SET HLD 100 ns min. PIC16F526 T 2 DLY Next Command 1 µs min PROG Next Command 1 2 DS41317B-page 5 ...

Page 6

... PIC16F526 3.1.2.5 End Programming After receiving this command, the chip stops programming the memory (User Program Memory, Flash Data Memory or Test Program Memory) it was programming at the time. FIGURE 3-6: END PROGRAMMING COMMAND V IHH MCLR RB1 (ICSPCLK) RB0 0 (ICSPDAT) Reset 3.1.2.6 Bulk Erase Program Memory After this command is performed, the specific section of Program Memory and Configuration Word is erased ...

Page 7

... Note: Yes = Erase No = Unchanged © 2007 Microchip Technology Inc. User Program Flash Data Memory Memory Erased Erased Yes CPDF = 0 – Yes CPDF = 1 – No Yes CPDF = 0 – Yes CPDF = 1 – CPDF = 0 – No CPDF = 1 – Yes No No PIC16F526 User ID Memory Erased Yes DS41317B-page 7 ...

Page 8

... PIC16F526 FIGURE 3-8: READING AND TEMPORARY SAVING OF THE OSCCAL CALIBRATION BITS Increment Address Increment Address DS41317B-page 8 Start Enter Programming Mode 0x3FF? Yes Read Calibration Bits and Save in Computer/Programmer Temp. Memory 0x444? Yes Read Backup OSCCAL Calibration Bits and Save in Computer/Programmer Temp. Memory ...

Page 9

... Yes Read Calibration Bits from Computer/Programmer Temp. Memory Write Calibration Bits back as the operand of a MOVLW instruction to 0x3FF 0x444? Yes Read Backup OSCCAL Calibration Bits from Computer/Programmer Temp. Memory Write Backup OSCCAL Bits back to 0x444 Exit Programming Mode Done PIC16F526 DS41317B-page 9 ...

Page 10

... PIC16F526 FIGURE 3-10: PROGRAM FLOWCHART – USER MEMORY Start Enter Programming Mode PC = 0x7FF (Config Word) Increment Address One Word Program Cycle Read Data from Program Memory Data Correct? Yes Increment No Address All Programming Command Locations Done? Exit Programming Mode Done DS41317B-page 10 ...

Page 11

... Increment No Address All Programming Command Locations Done? Exit Programming Mode Done © 2007 Microchip Technology Inc. Yes Report No Programming Failure Yes PIC16F526 PROGRAM CYCLE Load Data for Program Memory Begin Programming Command (Externally timed) Wait T PROG End Programming Wait T DIS DS41317B-page 11 ...

Page 12

... PIC16F526 FIGURE 3-12: PROGRAM FLOWCHART – CONFIGURATION MEMORY Start Enter Programming Mode PC = 0x7FF (Config Word) Load Data Command One-Word Programming Cycle (see Figure 3-10) Read Data Command Data Correct? Increment Address Command No Address = 0x440? Load Data Command One-Word Programming Cycle (see Figure 3-10) ...

Page 13

... PC = 0x7FF (Config. Word) Increment Address 0x400? Note 1: This operation requires that CPDF = 1. © 2007 Microchip Technology Inc. Bulk Erase Device Exit Programming Restore OSCCAL bits ) Yes PIC16F526 Wait T ERA Mode ( Figure 3-9 ) Done Bulk Erase Device Wait T ERA Exit Programming Mode ...

Page 14

... PIC16F526 FIGURE 3-15: PROGRAM FLOWCHART – ERASE USER ID Start Increment PC DS41317B-page 14 Read and save OSCCAL bits Figure 3 Enter Program/Verify mode PC = 0x7FF (Config. Word 0x440? (First User ID) Yes Bulk Erase Device Wait T ERA Exit Programming Mode Restore OSCCAL bits Figure 3 Done © 2007 Microchip Technology Inc. ...

Page 15

... PROGRAM FLOWCHART – HIGH-LEVEL FULL DEVICE PROGRAM © 2007 Microchip Technology Inc. Start Read OSCCAL bits Bulk Erase User Memory Bulk Erase Data Memory Bulk Erase ID/OSCCAL Program User Memory Program Data Memory Program Configuration Memory Restore OSCCAL bits Done PIC16F526 DS41317B-page 15 ...

Page 16

... PIC16F526 FIGURE 3-17: PROGRAM FLOWCHART – HIGH-LEVEL FULL DEVICE ERASE DS41317B-page 16 Start Read OSCCAL bits Bulk Erase User Memory Bulk Erase Data Memory Bulk Erase ID/OSCCAL Restore OSCCAL bits Done © 2007 Microchip Technology Inc. ...

Page 17

... It is the responsibility of the application designer to ensure the use of the 1 ms DRT will result in accept- able operation. Refer to Electrical Specifications for V of operation. © 2007 Microchip Technology Inc. bits can be CPDF IOSCFS MCLRE CP DD rise time and stability requirements for this mode DD PIC16F526 WDTE FOSC2 FOSC1 FOSC0 bit 0 (1) (1) (1) (1) (1) DS41317B-page 17 ...

Page 18

... Any Carry bits exceeding 16 bits are neglected. Finally, the Configuration Word (appropriately masked) is added to the checksum. The checksum computation for the PIC16F526 is shown in Table 5-1. Memory The checksum is calculated by summing the following: • The contents of all program memory locations • ...

Page 19

... PIC16F526 Max. Units Conditions 13 1 μs 1.0 — V 0.15 5.5 V 13.5 V 1.8 mA 1.8 mA 0.4 mA μs 2000 μ ...

Page 20

... PIC16F526 NOTES: DS41317B-page 20 © 2007 Microchip Technology Inc. ...

Page 21

... PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries. SQTP is a service mark of Microchip Technology Incorporated in the U.S.A. All other trademarks mentioned herein are property of their respective companies. ...

Page 22

... Fax: 886-3-572-6459 Taiwan - Kaohsiung Tel: 886-7-536-4818 Fax: 886-7-536-4803 Taiwan - Taipei Tel: 886-2-2500-6610 Fax: 886-2-2508-0102 Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350 © 2007 Microchip Technology Inc. EUROPE Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829 France - Paris Tel: 33-1-69-53-63-20 ...