CY7C68014A-56BAXC Cypress Semiconductor Corp, CY7C68014A-56BAXC Datasheet - Page 42

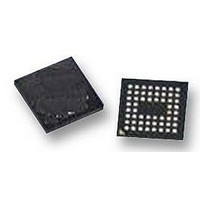

CY7C68014A-56BAXC

Manufacturer Part Number

CY7C68014A-56BAXC

Description

IC MCU USB PERIPH HI SPD 56VFBGA

Manufacturer

Cypress Semiconductor Corp

Series

EZ-USB FX2LP™r

Specifications of CY7C68014A-56BAXC

Applications

USB Microcontroller

Core Processor

8051

Program Memory Type

ROMless

Controller Series

CY7C680xx

Ram Size

16K x 8

Interface

I²C, USB, USART

Number Of I /o

24

Voltage - Supply

3 V ~ 3.6 V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

56-VFBGA

Core Size

16bit

No. Of I/o's

24

Program Memory Size

16KB

Ram Memory Size

16KB

Cpu Speed

48MHz

Oscillator Type

External Only

No. Of Timers

3

Digital Ic Case Style

VFBGA

Supply Voltage Range

3V

Controller Family/series

EZ-USB FX2LP

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

CY4611B - KIT USB TO ATA REFERENCE DESIGN

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY7C68014A-56BAXC

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

10.6 GPIF Synchronous Signals

Table 18. GPIF Synchronous Signals Parameters with Internally Sourced IFCLK

Table 19. GPIF Synchronous Signals Parameters with Externally Sourced IFCLK

Document #: 38-08032 Rev. *M

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

Notes

IFCLK

SRY

RYH

SGD

DAH

SGA

XGD

XCTL

IFCLK

SRY

RYH

SGD

DAH

SGA

XGD

XCTL

20. Dashed lines denote signals with programmable polarity.

21. GPIF asynchronous RDY

22. IFCLK must not exceed 48 MHz.

Parameter

Parameter

IFCLK Period

RDY

Clock to RDY

GPIF Data to Clock Setup Time

GPIF Data Hold Time

Clock to GPIF Address Propagation Delay

Clock to GPIF Data Output Propagation Delay

Clock to CTL

IFCLK Period

RDY

Clock to RDY

GPIF Data to Clock Setup Time

GPIF Data Hold Time

Clock to GPIF Address Propagation Delay

Clock to GPIF Data Output Propagation Delay

Clock to CTL

x

signals have a minimum Setup time of 50 ns when using internal 48-MHz IFCLK.

X

X

to Clock Setup Time

to Clock Setup Time

GPIFADR[8:0]

DATA(output)

DATA(input)

X

X

Figure 17. GPIF Synchronous Signals Timing Diagram

X

[22]

X

Output Propagation Delay

Output Propagation Delay

IFCLK

RDY

CTL

X

X

Description

Description

t

SRY

t

SGD

t

XCTL

N

t

XGD

t

IFCLK

valid

t

RYH

t

t

DAH

SGA

N+1

20.83

20.83

Min.

Min

8.9

9.2

2.9

3.7

3.2

4.5

0

0

CY7C68013A, CY7C68014A

CY7C68015A, CY7C68016A

[20, 21]

[21]

[20]

Max.

Max

11.5

10.7

200

7.5

6.7

11

15

Page 42 of 62

Unit

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

[+] Feedback