KSZ8851SNL TR Micrel Inc, KSZ8851SNL TR Datasheet - Page 59

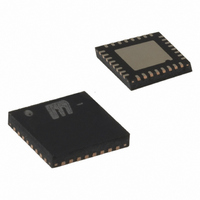

KSZ8851SNL TR

Manufacturer Part Number

KSZ8851SNL TR

Description

IC CTLR MAC/PHY NON-PCI 32-MLF

Manufacturer

Micrel Inc

Specifications of KSZ8851SNL TR

Controller Type

Ethernet Controller, MAC/PHY

Interface

Bus

Voltage - Supply

1.8V, 2.5V, 3.3V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

32-MLF®, QFN

Operating Supply Voltage (typ)

3.3V

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

32

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

576-3293 - BOARD EVALUATION KSZ8851SNL

Current - Supply

-

Lead Free Status / RoHS Status

Supplier Unconfirmed, Lead free / RoHS Compliant

Other names

576-3299-2

Flow Control High Watermark Register (0xB2 – 0xB3): FCHWR

This register is used to control the flow control for high watermark in QMU RX queue.

Flow Control Overrun Watermark Register (0xB4 – 0xB5): FCOWR

This register is used to control the flow control for overrun watermark in QMU RX queue

0xB6 – 0xBF: Reserved

Chip ID and Enable Register (0xC0 – 0xC1): CIDER

This register contains the chip ID and the chip enable bit.

0xC2 – 0xC5: Reserved

Chip Global Control Register (0xC6 – 0xC7): CGCR

This register contains the global control for the chip function.

Indirect Access Control Register (0xC8 – 0xC9): IACR

This register contains the indirect control for the MIB counter (Write IACR triggers a command. Read access is

determined by bit 12).

August 2009

Micrel, Inc.

Bit

15-12

11-0

Bit

15-12

11-0

Bit

15-8

7-4

3-1

0

Bit

15-12

11-10

9

8

7-0

-

-

0x0

0x0

0x0

Default Value

0x0300

Default Value

0x0040

Default

0x88

0x7

0x1

Default

0x0

0x2

0x35

R/W

RW

RW

R/W

RW

RW

R/W

RO

RO

RO

RW

R/W

RW

RW

RW

R/W

RW

Description

Reserved

FCHWC Flow Control High Watermark Configuration

These bits are used to define the QMU RX queue high watermark configuration. It is in

double words count and default is 3.072 KByte available buffer space out of 12 KByte.

Description

Reserved

FCLWC Flow Control Overrun Watermark Configuration

These bits are used to define the QMU RX queue overrun watermark configuration. It is in

double words count and default is 256 Bytes available buffer space out of 12 Kbyte.

Description

Family ID

Chip family ID

Chip ID

0x7 is assigned to KSZ8851SNL

Revision ID

Reserved

Description

Reserved

Reserved

LEDSEL0

This bit sets the LEDSEL0 selection for LED1 and LED0.

PHY port LED indicators, defined as below:

Reserved

Reserved

LED1 (pin32)

LED0 (pin1)

LINK/ACT

100BT

0

59

LEDSEL0

LINK

ACT

1

KSZ8851SNL/SNLI

M9999-083109-2.0