DS21FF42 Maxim Integrated Products, DS21FF42 Datasheet - Page 25

DS21FF42

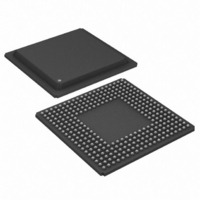

Manufacturer Part Number

DS21FF42

Description

IC FRAMER T1 4X4 16CH 300-BGA

Manufacturer

Maxim Integrated Products

Datasheet

1.DS21FT42.pdf

(114 pages)

Specifications of DS21FF42

Controller Type

T1 Framer

Interface

Parallel/Serial

Voltage - Supply

2.97 V ~ 3.63 V

Current - Supply

300mA

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

300-BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

DS21FF42

Manufacturer:

LATTRON

Quantity:

9 020

This signal is used to asynchronously reset the test access port controller. At power up, JTRST* must be

set low and then high. This action will set the device into the DEVICE ID mode allowing normal device

operation. If boundary scan is not used and FMS = 0, this pin should be held low. This function is

available when FMS = 0. When FMS=1, this pin is held LOW internally. This pin is pulled up internally

by a 10K ohm resistor. FMS is tied to ground for the DS21FF42/DS21FT42.

This pin is sampled on the rising edge of JTCLK and is used to place the test port into the various defined

IEEE 1149.1 states. This pin is pulled up internally by a 10K ohm resistor. If not used, this pin should

be left unconnected. This function is available when FMS = 0. FMS is tied to ground for the

DS21FF42/DS21FT42.

This signal is used to shift data into JTDI pin on the rising edge and out of JTDO pin on the falling edge.

If not used, this pin should be connected to VSS. This function is available when FMS = 0. FMS is tied

to ground for the DS21FF42/DS21FT42.

Test instructions and data are clocked into this pin on the rising edge of JTCLK. This pin is pulled up

internally by a 10K ohm resistor. If not used, this pin should be left unconnected. This function is

available when FMS = 0. FMS is tied to ground for the DS21FF42/DS21FT42.

Test instructions and data are clocked out of this pin on the falling edge of JTCLK. If not used, this pin

should be left unconnected. This function is available when FMS = 0. FMS is tied to ground for the

DS21FF42/DS21FT42.

SUPPLY PINS

2.97 to 3.63 volts.

Signal Name:

Signal Description:

Signal Type:

Signal Name:

Signal Description:

Signal Type:

Signal Name:

Signal Description:

Signal Type:

Signal Name:

Signal Description:

Signal Type:

Signal Name:

Signal Description:

Signal Type:

Signal Name:

Signal Description:

Signal Type:

JTRST*

IEEE 1149.1 Test Reset

Input

JTMS

IEEE 1149.1 Test Mode Select

Input

JTCLK

IEEE 1149.1 Test Clock Signal

Input

JTDI

IEEE 1149.1 Test Data Input

Input

JTDO

IEEE 1149.1 Test Data Output

Output

VDD

Positive Supply

Supply

25 of 114