MC68HC711KS2MFN4 Freescale Semiconductor, MC68HC711KS2MFN4 Datasheet - Page 55

MC68HC711KS2MFN4

Manufacturer Part Number

MC68HC711KS2MFN4

Description

32K EPROM - SLOW MODE

Manufacturer

Freescale Semiconductor

Datasheet

1.MC68HC711KS2MFN4.pdf

(290 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC68HC711KS2MFN4

Manufacturer:

Freescale

Quantity:

300

- Current page: 55 of 290

- Download datasheet (2Mb)

3.6.5 Inherent

3.6.6 Relative

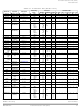

3.7 Instruction Set

M68HC11K Family

MOTOROLA

In the inherent addressing mode, the opcode contains all required

information. The operands (if any) are registers, so no memory access

is required. This mode includes:

These instructions are one or two bytes.

Only branch instructions use the relative addressing mode. If the branch

condition is true, the CPU adds the 8-bit signed offset following the

opcode to the contents of the program counter to form the effective

branch address. Otherwise, control proceeds to the next instruction.

These are usually 2-byte instructions.

Table 3-1

all possible addressing modes.

•

•

Control instructions with no arguments

Operations that only involve the index registers or accumulators

presents a detailed listing of all the M68HC11 instructions in

Central Processor Unit (CPU)

Central Processor Unit (CPU)

Technical Data

Instruction Set

55

Related parts for MC68HC711KS2MFN4

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

APPENDIX A ELECTRICAL CHARACTERISTICS

Manufacturer:

FREESCALE [Freescale Semiconductor, Inc]

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: