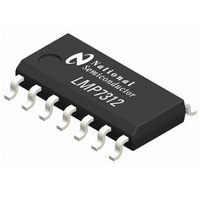

LMP7312MA/NOPB National Semiconductor, LMP7312MA/NOPB Datasheet - Page 15

LMP7312MA/NOPB

Manufacturer Part Number

LMP7312MA/NOPB

Description

IC AMP PROGRAM AFE 14SOIC

Manufacturer

National Semiconductor

Type

Programmable Amplifier/Attenuatorr

Datasheet

1.LMP7312MANOPB.pdf

(22 pages)

Specifications of LMP7312MA/NOPB

Input Type

Logic

Output Type

Logic

Interface

SPI

Current - Supply

2mA

Mounting Type

Surface Mount

Package / Case

14-SOIC (3.9mm Width), 14-SOL

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

LMP7312MA

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LMP7312MA/NOPB

Manufacturer:

Intersil

Quantity:

840

INPUT VOLTAGE RANGE

The LMP7312 has an internal OpAmp with rail-to-rail input

voltage range capability. The requirement to stay within the

V

age Range specification as explained in this application sec-

tion.

Differential Output

Considering a single positive supply (V

Input Common mode voltage, V

the Attenuation inputs and V

Amplification inputs, has to stay between the MIN and MAX

values determined by these formulas:

CM

CM

K

Regardless to the values derived by the formula, the voltage

on each input pin must never exceed the specified Absolute

Maximum Ratings.

Below are some typical values:

Differential Input, Differential Output, V

* Limited by the operating ratings on input pins

In the case of a single ended input referred to ground (-V

GND, -IN = GND) the table below summarizes the voltage

range allowed on the +VI

Single Ended Input, Differential Output, V

2.5V, -V

* Limited by the operating ratings on input pins

** Limited by the output voltage swing (0.2V to V

-V

Single Ended Output

In this mode the LMP7312 behaves as a Difference Amplifier,

with -V

volt differential input signal is applied. The voltages at the

OpAmp inputs are determined by +V

The voltage range of +V

V

Gain 0.096 V/

K

-

V

MAX

OUT

V

0.096 V/V

0.192 V/V

0.384 V/V

0.768 V/V

and V

0.096 V/V

0.192 V/V

0.384 V/V

0.768 V/V

is a function of the Gain according to the table below:

MAX

MIN

)

1 V/V

2 V/V

Gain

1 V/V

2 V/V

Gain

= V

OUT

V

0.12

= -1/K

= V

IN

+

S

rail at the OpAmp input translates in an Input Volt-

/V

= GND, -I

+ 1/ K

S

R

+ 1/K

V

being the reference output voltage when a zero

*V

OCM

-12 V

V

0.192 V/

V

0.218

-15 V

-15 V

-6 V

V

-11.5 V

Min

* (V

-15 V

-3.1 V

*(V

-6 V

Min

IN

**

**

S

= GND

S

*

*

V

+V

– (-V

- V

*

IN

CM_ATT

N

IN

and +I

and +I

OCM

0.384 V/

V

0.414

+12 V

+15 V

+15 V

+6 V

CM_AMP

Max

OUT

+15 V

+8.1 V

+15 V

+11 V

)

Max

CM_ATT

/V

**

IN

IN

**

*

*

R

inputs is as follows:

inputs.

IN

))

*

= (+I

0.768 V/

V

0.806

and -V

-

-4.6 V

-2.3 V

S

= (+V

-0.2V on both + V

= GND, V

Min

-2.3 V

-1.2 V

S

IN

Min

= 5V, V

+ (-I

OUT

S

IN

**

**

V

= 5V, V

+IN

+ (-V

CM_AMP

1 V/V 2 V/V

1.065 2.096

/V

IN

))/2 for the

OCM

+

R

+4.6 V

+2.3 V

= V

voltages.

+7.3 V

+6.2 V

IN

Max

Max

OCM

))/2 for

= 2.5V

OUT

S

) the

IN

**

**

and

=

=

15

V

Regardless of the values derived by the formula, the voltage

on each input pin must never exceed the specified Absolute

Maximum Ratings.

Below are some typical values:

Differential Input, Single Ended Output, V

GND, and -V

* Limited by the operating ratings on input pins

In the case of a single ended input referred to ground (-V

GND, -IN = GND) this table summarize the voltage ranges

allowed on the +V

Single Ended Input, Single Ended Output, V

= GND, -V

* Limited by the operating ratings on input pins

** Limited by the output voltage swing (0.2V to V

SERIAL INTERFACE CONTROL OPERATION

The serial interface control of the LMP7312 can be supplied

with a voltage between 2.7V and 5.5V through the V

compatibility with different logic families present in the market.

The LMP7312 Attenuation, Amplification, Null switch and HiZ

modes are controlled by a register. Data to be written into the

control register is first loaded into the LMP7312 via the serial

interface. The serial interface employs a 5-bit shift register.

Data is loaded through the serial data input, SDI. Data pass-

ing through the shift register is obtained through the serial

data output, SDO. The serial clock, SCK controls the serial

loading process. All five data bits are required to correctly

program the device. The falling edge of CS enables the shift

register to receive data. The SCK signal must be high during

the falling edge of CS. Each data bit is clocked into the shift

register on the rising edge of SCK. Data is transferred from

the shift register to the holding register on the rising edge of

CS. Operation is shown in the timing diagram .

SPI Registers

0.096 V/V

0.192 V/V

0.384 V/V

0.768 V/V

1 V/V

2 V/V

MIN

0.096 V/V

0.192 V/V

0.384 V/V

0.768 V/V

Gain_1

MSB

Gain

= -1/K

1 V/V

2 V/V

Gain

OUT

V

* (-V

OUT

/V

Gain_0

-15 V

-11.5 V

-6 V

-3 V

R

/V

OUT

= 2.5V, -V

-11.5 V

IN

Min

R

-15 V

-3.1 V

**

**

Min

-6 V

and +I

= 2.5V

*

/V

R

+V

)

*

+V

*

IN

EN_CL

IN

+15 V

+12 V

+6 V

+3 V

IN

IN

inputs.

Max

= GND, -I

+15 V

+8.1 V

+15 V

+11 V

**

**

Max

*

**

*

Null_SW

-2.3 V

-1.1 V

S

IN

-0.2V on +V

Min

-2.3 V

-1.2 V

= GND

Min

**

**

S

= 5V, V

S

+I

+I

www.national.com

= 5V, V

IN

+2.3 V

+1.1 V

OUT

IN

Hi_Z

LSB

+7.3 V

+6.2 V

IO

Max

Max

)

OCM

pin for

**

**

OCM

IN

=

=