PX1011B-EL1/N,557 NXP Semiconductors, PX1011B-EL1/N,557 Datasheet

PX1011B-EL1/N,557

Specifications of PX1011B-EL1/N,557

PX1011B-EL1/N

PX1011B-EL1/N

Available stocks

Related parts for PX1011B-EL1/N,557

PX1011B-EL1/N,557 Summary of contents

Page 1

... PHYsical layer (PHY) that handles the low level PCI Express protocol and signaling. The PX1011B PCI Express PHY is compliant to the PCI Express Base Specification, Rev. 1.0a , and Rev. 1.1 . The PX1011B includes features such as Clock and Data Recovery (CDR), data serialization and de-serialization, 8b/10b encoding, analog buffers, elastic buffer and receiver detection, and provides superior performance to the Media Access Control (MAC) layer devices ...

Page 2

... I/O and PVT analog supply voltage 1 for serializer analog supply voltage 2 for serializer reference clock frequency ambient temperature operating commercial industrial Rev. 04 — 4 September 2009 PX1011B PCI Express stand-alone X1 PHY Min Typ Max Unit 3.0 3.3 3.6 V 2.3 2.5 2 ...

Page 3

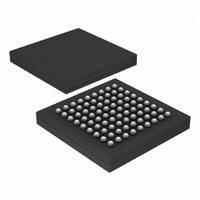

... NXP Semiconductors 4. Ordering information Table 2. Ordering information Type number Solder process PX1011B-EL1/G Pb-free (SnAgCu solder ball compound) PX1011B-EL1/N SnPb solder ball compound PX1011BI-EL1/G Pb-free (SnAgCu solder ball compound) 5. Marking Table 3. Line Table 4. Line [1] Industrial temperature range. PX1011B_4 Product data sheet Package ...

Page 4

... PARALLEL TO SERIAL 250 MHz clock CLK GENERATOR TX I/O REFCLK I/O TX_P TX_N REFCLK_P REFCLK_N Block diagram Rev. 04 — 4 September 2009 PX1011B PCI Express stand-alone X1 PHY PCI Express MAC RXDATA [ 7:0 ] RESET_N PCI Express PHY REGISTER 8 10b/8b DECODE ELASTIC BUFFER 10 K28.5 SERIAL ...

Page 5

... V V DDD2 SS DDD2 DDA2 DDA1 V TMS V DDD1 DDD1 TCK TRST_N V DDD3 TDI DDD2 TDO TXIDLE V SS RESET_N RXPOL TXCOMP Rev. 04 — 4 September 2009 PX1011B PCI Express stand-alone X1 PHY 002aad017 RXDATA1 RXDATAK RXCLK RXDATA2 RXDATA0 RXVALID SS DDD2 PVT V PHYSTATUS DDD3 DDD2 TXDATA3 ...

Page 6

... J4 input SSTL_2 J3 input SSTL_2 H6 input SSTL_2 J6 input SSTL_2 Rev. 04 — 4 September 2009 PX1011B PCI Express stand-alone X1 PHY Table 5 to Table 12. Note that input and Signaling Description PCIe I/O differential input receive pair with 50 on-chip termination PCIe I/O PCIe I/O differential output transmit pair with ...

Page 7

... V CMOS G3 input 3.3 V CMOS H3 output 3.3 V CMOS Rev. 04 — 4 September 2009 PX1011B PCI Express stand-alone X1 PHY Description indicates symbol lock and valid data on RX_DATA and RX_DATAK used to communicate completion of several PHY functions including power management state transitions and receiver detection indicates receiver detection of an electrical idle ...

Page 8

... Clock and Data Recovery (CDR), data serialization and de-serialization, 8b/10b encoding, analog buffers, elastic buffer and receiver detection. The PXPIPE interface between the MAC and PX1011B is a superset of the PHY Interface for the PCI Express (PIPE) specification. The following feature have been added: • ...

Page 9

... The PLL has a sufficiently high bandwidth to handle a 100 MHz reference clock with a 30 kHz to 33 kHz spread spectrum. 8.3 Clocking There are three clock signals used by the PX1011B: • REFCLK is a 100 MHz external reference clock that the PHY uses to generate the 250 MHz data clock and the internal bit rate clock ...

Page 10

... L1.idle state of the Link Training and Status State Machine (LTSSM). • P2 state: PHY will enter P1 instead. PX1011B_4 Product data sheet RXCLK Reset Rev. 04 — 4 September 2009 PX1011B PCI Express stand-alone X1 PHY 100 MHz 250 MHz © NXP B.V. 2009. All rights reserved. 002aac172 ...

Page 11

... SKP symbol. PX1011B_4 Product data sheet Transmitter [1] on [2] idle [2] idle - TXCLK 10b RXCLK 000b Receiver detect - receiver present Rev. 04 — 4 September 2009 PX1011B PCI Express stand-alone X1 PHY Receiver TX PLL RXCLK idle on on idle ...

Page 12

... TXCLK Tx-m Tx-n RXCLK Rx-c Rx-d TX_P, TX_N Loopback start Figure 7 shows an example of switching from loopback mode to Rev. 04 — 4 September 2009 PX1011B PCI Express stand-alone X1 PHY Tx-o Tx-p Tx-q Rx-e Rx-f Rx-g Tx-m Tx-n Rx-e © NXP B.V. 2009. All rights reserved. ...

Page 13

... Loopback end Figure 8 shows an example of timing for entering electrical idle. ScZero COM active (ends with Electrical Idle ordered-set) Electrical Idle Rev. 04 — 4 September 2009 PX1011B PCI Express stand-alone X1 PHY Junk Junk IDL © NXP B.V. 2009. All rights reserved. 001aac785 002aac175 ...

Page 14

... PHY removed a SKP symbol from a SKP RXCLK active COM RXVALID 000b 001b Clock correction - insert a SKP Rev. 04 — 4 September 2009 PX1011B PCI Express stand-alone X1 PHY Function description normal operation transmitter in idle loopback mode illegal illegal transmitter in idle ...

Page 15

... Elastic buffer overflow 3. Elastic buffer underflow 4. Disparity error PX1011B_4 Product data sheet RXCLK active COM RXVALID 000b 010b Function table PXPIPE status interface signals Rev. 04 — 4 September 2009 PX1011B PCI Express stand-alone X1 PHY SKP active 000b Output pin RXSTATUS2 RXSTATUS1 RXSTATUS0 ...

Page 16

... Rx-a Rx-b RXVALID 000b the receiver detected a disparity error on Rx-c data byte, and indicates this with RXCLK Rx-a Rx-b RXVALID 000b Figure Rev. 04 — 4 September 2009 PX1011B PCI Express stand-alone X1 PHY EDB Rx-d Rx-e 100b 000b Rx-c Rx-d Rx-e 111b 000b 13, the PHY is receiving a repeating set of © ...

Page 17

... Rx-b RXVALID 000b RXCLK Rx-a Rx-b RXVALID 000b RXCLK D21.5 D21.5 RXVALID RXPOL Rev. 04 — 4 September 2009 PX1011B PCI Express stand-alone X1 PHY Rx-c EDB Rx-d 110b 000b Rx-c Rx-e Rx-f 101b 000b D10.2 D10.2 © NXP B.V. 2009. All rights reserved. ...

Page 18

... TRST_N to V PX1011B_4 Product data sheet TXCLK data K28.5 TXCOMP valid data . SS Rev. 04 — 4 September 2009 PX1011B PCI Express stand-alone X1 PHY K28.5 K28.5 K28.5 byte transmitted with negative disparity K28.5 K28.5 © NXP B.V. 2009. All rights reserved. 002aac177 ...

Page 19

... Thermal characteristics Parameter thermal resistance from junction to ambient thermal resistance from junction to case Rev. 04 — 4 September 2009 PX1011B PCI Express stand-alone X1 PHY Conditions Min for JTAG I/O 0.5 for SSTL_2 I/O 0.5 for core ...

Page 20

... JTAG I/O for SSTL_2; no load for core for high-speed serial I/O and PVT for serializer for serializer 1 clock cycle Rev. 04 — 4 September 2009 PX1011B PCI Express stand-alone X1 PHY Min Typ Max Unit 3.0 3.3 3.6 V 2.3 2 ...

Page 21

... Figure 17 at falling edge; measured from +150 mV to 150 mV on the differential waveform; Figure 17 on pin REFCLK_N and pin REFCLK_P 1 clock cycle Rev. 04 — 4 September 2009 PX1011B PCI Express stand-alone X1 PHY Min Typ Max Unit 0.6 - 4.0 V/ns 0 ...

Page 22

... Figure 18 see Figure 18 see Figure 18 see Figure 18 TXCLK PXPIPE INPUT t su(TX)(PXPIPE) RXCLK PXPIPE OUTPUT Rev. 04 — 4 September 2009 PX1011B PCI Express stand-alone X1 PHY dV/dt at falling edge 002aad694 Min Typ Max 249.925 250 250.075 249.925 250 250.075 [1] 1.13 1.25 1. ...

Page 23

... Rev. 04 — 4 September 2009 PCI Express stand-alone X1 PHY 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0 unit intervals 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0 unit intervals PX1011B 001aac789 1.1 1.2 001aac790 1.1 1.2 © NXP B.V. 2009. All rights reserved ...

Page 24

... 9.1 9.1 0.8 6.4 6.4 0.15 8.9 8.9 REFERENCES JEDEC JEITA MO-205 - - - Rev. 04 — 4 September 2009 PCI Express stand-alone X1 PHY detail 0.08 0.12 0.1 EUROPEAN PROJECTION PX1011B SOT643-1 ISSUE DATE 00-11-01 02-03-28 © NXP B.V. 2009. All rights reserved ...

Page 25

... Solder bath specifications, including temperature and impurities PX1011B_4 Product data sheet Rev. 04 — 4 September 2009 PX1011B PCI Express stand-alone X1 PHY © NXP B.V. 2009. All rights reserved ...

Page 26

... Lead-free process (from J-STD-020C) Package reflow temperature ( C) 3 Volume (mm ) < 350 260 260 250 Figure 22. Rev. 04 — 4 September 2009 PX1011B PCI Express stand-alone X1 PHY Figure 22) than a SnPb process, thus 350 220 220 350 to 2000 > 2000 260 260 250 245 245 245 © ...

Page 27

... L0s and enters L0), the PX1011B receiver PLL may randomly fail to lock, preventing it from properly interpreting the data being transmitted on the link result the PX1011B may send symbols to the link device that it cannot recognize. This is a L0s exit failure which may prevent the system from recovering and could cause the PCIe protocol to eventually fail and the link to go down. If this occurs, the PX1011B stays in the exit failure state indefi ...

Page 28

... Modifications: Section 14: Errata information added PX1011B_3 20081020 • Modifications: Added type number PX1011B-EL1/N (affects Section 2.6 “Miscellaneous”, Table 2 “Ordering information”, (new) Table 3 “Leaded package marking”, Figure 2 “Pin configuration for LFBGA81”) PX1011B_2 20080319 PX1011B_1 20080213 PX1011B_4 ...

Page 29

... Trademarks Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners. http://www.nxp.com salesaddresses@nxp.com Rev. 04 — 4 September 2009 PX1011B PCI Express stand-alone X1 PHY © NXP B.V. 2009. All rights reserved ...

Page 30

... Please be aware that important notices concerning this document and the product(s) described herein, have been included in section ‘Legal information’. © NXP B.V. 2009. For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com PX1011B All rights reserved. Date of release: 4 September 2009 Document identifier: PX1011B_4 ...