SAA7196H NXP Semiconductors, SAA7196H Datasheet

SAA7196H

Available stocks

Related parts for SAA7196H

SAA7196H Summary of contents

Page 1

DATA SHEET SAA7196 Digital video decoder, Scaler and Clock generator circuit (DESCPro) Product specification File under Integrated Circuits, IC22 INTEGRATED CIRCUITS 1996 Nov 04 ...

Page 2

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) CONTENTS 1 FEATURES 2 GENERAL DESCRIPTION 3 QUICK REFERENCE DATA 4 ORDERING INFORMATION 5 BLOCK DIAGRAM 6 PINNING 7 FUNCTIONAL DESCRIPTION 7.1 Decoder part 7.1.1 Chrominance processor 7.1.2 Luminance ...

Page 3

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 1 FEATURES Digital 8-bit luminance input [video (Y) or CVBS] Digital 8-bit chrominance input [CVBS or C from CVBS, Y/C, S-Video (S-VHS or Hi8)] Luminance and chrominance signal processing ...

Page 4

... O f input clock frequency BCK T operating ambient temperature amb 4 ORDERING INFORMATION TYPE NUMBER NAME SAA7196H QFP120 1996 Nov 04 2 C-bus interface is The programming of the subaddresses for the scaler part becomes effective at the first Vertical Sync (VS) pulse after a transmission. PARAMETER PACKAGE DESCRIPTION plastic quad fl ...

Page 5

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 5 BLOCK DIAGRAM 1996 Nov 04 5 Product specification SAA7196 pagewidth full handbook, ...

Page 6

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 1996 Nov 04 6 Product specification SAA7196 pagewidth full handbook, ...

Page 7

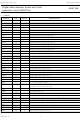

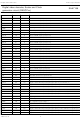

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 6 PINNING SYMBOL PIN STATUS XTAL 1 XTALI 2 SDA 3 SCL CSA 5 CHR0 6 CHR1 7 CHR2 8 CHR3 9 CHR4 10 CHR5 11 ...

Page 8

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) SYMBOL PIN STATUS CREFB 39 LLC 40 LLCB 41 LLC2 42 BTST 43 RTCO DDD3 VMUX SSD3 SODD 48 SVS 49 SHREF 50 ...

Page 9

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) SYMBOL PIN STATUS VRO19 71 VRO18 72 VRO17 73 VRO16 SSD5 i. DDD5 VRO15 78 VRO14 79 VRO13 80 VRO12 81 VRO11 82 ...

Page 10

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) SYMBOL PIN STATUS YUV2 112 YUV1 113 YUV0 114 HREF 115 VS 116 HS 117 AP 118 SP 119 V 120 SSD7 1996 Nov 04 I/O digital 16-bit video ...

Page 11

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) handbook, full pagewidth XTAL 1 XTALI 2 SDA 3 SCL CSA 5 CHR0 6 CHR1 7 CHR2 8 CHR3 9 10 CHR4 CHR5 11 CHR6 12 ...

Page 12

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 7 FUNCTIONAL DESCRIPTION 7.1 Decoder part PAL, NTSC and SECAM standard colour signals based on line-locked clock are decoded (see Fig.27). In Y/C mode, digitized luminance CVBS7 to CVBS0 ...

Page 13

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) Mode 3: YUV15 to YUV0 and HREF/VS terminals are inputs. External YUV15 to YUV0 is input to the scaler with HREF/VS reference from external. LLCB/CREFB clock system of the ...

Page 14

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 7.3 Monitor controls BCS 7.3.1 B RIGHTNESS AND CONTRAST CONTROLS The luminance signal can be controlled via I (see Table 16) by the bits BRIG7 to BRIG0 and CONT6 ...

Page 15

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) Table 5 YUV-bus format on expansion port; note 1 PIN n YUV15 Ye7 YUV14 Ye6 YUV13 Ye5 YUV12 Ye4 YUV11 Ye3 YUV10 Ye2 YUV9 Ye1 YUV8 Ye0 YUV7 Ue7 ...

Page 16

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) handbook, full pagewidth LLCB CREFB HREF DIR UV dec (from decoder) UV ext (from external port scaler t = 1.5LLC + t from 3-state(min) PZ(min) t > ...

Page 17

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 625 1 handbook, full pagewidth input CVBS HREF VS ODD (RTSO) 313 handbook, full pagewidth input CVBS HREF VS ODD (RTSO) 1996 Nov 1st ...

Page 18

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 525 1 handbook, full pagewidth input CVBS HREF VS ODD (RTSO) 263 handbook, full pagewidth input CVBS HREF VS ODD (RTSO) 1996 Nov 1st ...

Page 19

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) handbook, full pagewidth CVBS HSY (1) 191 HSY programming range (step size: 2/LLC) HCL (1) 127 HCL programming range (step size: 2/LLC) processing delay CVBS - YUV Y output ...

Page 20

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) LLCB CREFB HREF Byte numbers for pixels: Y signal and V signal Y signal and V signal LLCB CREFB HREF Byte numbers for ...

Page 21

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) handbook, full pagewidth digital signal value 254 white 100% 235 128 luminance levels black signal range. Fig.10 Input and output signal levels on expansion port. ...

Page 22

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) handbook, full pagewidth H/L transition (counter start) 128 clock cycles RTCO (1) Sequence bit: SECAM: 0 equals DB-line; 1 equals DR-line. PAL: 0 equals (R Y) line normal; 1 ...

Page 23

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 7.4.1 D ECIMATION FILTERS The decimation filters perform accurate horizontal filtering of the input data stream. The signal bandwidth is matched in front of the pixel decimation stage, thus ...

Page 24

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 7.4.5.1 Vertical bypass region Data are not scaled and independent of I FS0; the output format is always 8-bit gray scale (monochrome). The SAA7196 outputs all active pixels of ...

Page 25

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 7.4.6 O UTPUT DATA REPRESENTATION AND LEVELS Output data representation of the YUV data can be modified by bit MCT (subaddress 30). The DC gain is 1 for YUV ...

Page 26

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) It means: HFL = 1 at the rising edge of INCADR: the ‘end of line’ is reached; request for line address increment HFL = 0 at the rising edge ...

Page 27

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) Table 8 VRAM port output data formats for bits (continued in Table 9) EFE-bit = 0 and VOF-bit = 1 (controllable via I FS1 = 0; ...

Page 28

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) Table 9 VRAM port output data formats for bits (continued from Table 8) EFE-bit = 0 and VOF-bit = 1 (controllable via I FS1 = 0; ...

Page 29

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) Table 10 VRAM port output data formats for bits (continued in Table 11) EFE-bit = 1 and VOF-bit = 1 (controllable via I FS1 = 0; ...

Page 30

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) Table 11 VRAM port output data formats for bits (continued from Table 10) EFE-bit = 1 and VOF-bit = 1 (controllable via I FS1 = 0; ...

Page 31

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) Table 12 VRAM port output formats for bits (continued in Table 13) EFE-bit = 0 and VOF-bit = 0 (controllable via I FS1 = 0; FS0 ...

Page 32

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) Table 13 VRAM port output data formats for bits (continued from Table 12) EFE-bit = 0 and VOF-bit = 0 (controllable via I FS1 = 0; ...

Page 33

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) PIXCLK handbook, full pagewidth 1/2LLC FIFO memory 7 filling level HFL VCLK VOE VRO(n) (1) Minimum 8 words available in FIFO. (2) Maximum 32LLC (16PIXCLK). (3) 1 transfer cycle ...

Page 34

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) line n line n handbook, full pagewidth active internal signal video last half-full request for line n HFL 64LLC INCADR (1) Pulse only at interlace scan. handbook, full pagewidth ...

Page 35

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) handbook, full pagewidth SET SCALING ACTIVE IN CONTROL STAGE 1996 Nov 04 EXTERNAL RESET, VPE = 0 no VERTICAL SYNC DETECTED yes COEFFICIENT UPDATE no VPE = 1 yes ...

Page 36

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 7.4.11 F IELD PROCESSING The phase of the field sequence (odd/even dependent on inputs HREF and VS) is detected by means of the falling edge of VS. The current ...

Page 37

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 8 PROGRAMMING MODEL 2 8.1 I C-bus format (1) (2) S SLAVE ADDRESS Notes 1. START condition 0100 000X (I CSA = LOW) or 0100 001X (I ...

Page 38

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 2 8.2 I C-bus status information 2 Table 14 I C-bus status byte (X in address byte = 1; 41H at I FUNCTION Status byte 0 (transmitted after RES ...

Page 39

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 8.3 Decoder part 2 Table 16 I C-bus decoder control; subaddress and data bytes for writing (X in address byte = 0; 40H 42H at ...

Page 40

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) Table 17 Function of the register bits of Table 16 for subaddresses ‘00’ to ‘19’ SUBADDRESS IDEL7 to IDEL0 Increment delay time (dependent on application), step size = 4/LLC. ...

Page 41

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) SUBADDRESS CKTQ4 to CKTQ0 Colour-killer threshold QAM (PAL, NTSC) from approximately equals data ‘08’ bytes F8H to 07H. CKTS4 to CKTS0 Colour-killer threshold SECAM ...

Page 42

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) SUBADDRESS CHRS S-VHS bit (chrominance from CVBS or from chrominance input) ‘0E’ controlled by bit BYPS (subaddress 06 chrominance from chrominance input CHR7 to CHR0 ...

Page 43

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) SUBADDRESS HC6S7 to HC6S0 Horizontal clamp stop for 60 Hz, step size = 2/LLC. The delay time is selectable from ‘17’ 254/LLC (+127 decimal multiplier) to +256/LLC ( 128 ...

Page 44

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) Table 21 Automatic gain control (AGC filter) LFIS1 Table 22 General purpose switches GPSW2 (PIN 32 Table 23 Luminance delay compensation ...

Page 45

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) Table 24 Vertical noise reduction VNOI1 Table 25 Chrominance gain control; note ...

Page 46

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) Table 26 Chrominance saturation control for VRAM port Table 27 Luminance ...

Page 47

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) handbook, halfpage The tresholds are related to the 13-bit word width in the luminance processing part and influence the 1LSB to 3LSB (Y0 to Y2) with respect to the ...

Page 48

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 18 handbook, full pagewidth V Y (dB (1) 43H. (2) 53H. Fig.19 Luminance control in 50 Hz/CVBS mode ...

Page 49

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 18 handbook, full pagewidth V Y (dB) ( (1) 00H. (2) 03H. Fig.21 Luminance control in 50 Hz/CVBS mode ...

Page 50

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 18 handbook, full pagewidth V Y (dB) ( (1) 40H. (2) 41H. Fig.23 Luminance control in 60 Hz/CVBS ...

Page 51

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 18 handbook, halfpage V Y (dB ( (1) 80H. (2) 81H. (3) 82H. Fig.25 Luminance control in 50 Hz/S-VHS mode ...

Page 52

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 8.4 Scaler part 2 Table 29 I C-bus scaler control; subaddress and data bytes for writing FUNCTION SUBADDRESS Formats and sequence (2) Output data pixel/line (2) Input data pixel/line ...

Page 53

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) Table 30 Function of the register bits of Table 29 for subaddresses ‘20’ to ‘30’ SUBADDRESS RTB ROM table bypass switch ‘20’ anti-gamma ROM active 1 = ...

Page 54

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) VC8 to VC0 vertical bypass count, sets length of bypass region (straight binary) ‘29 and 2B’ 0 0000 0000; 0 line length 1 1111 1111; 511 lines length (maximum ...

Page 55

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) QPP pixel qualifier polarity fl PXQ is active-LOW (pin 51 PXQ is active-HIGH TTR transparent data transfer 0 = normal operation (VRAM data burst transfer) ...

Page 56

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) Table 34 FIFO output register format select (bit EFE; see ‘30’) EFE FS1 FS0 ...

Page 57

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 10 handbook, full pagewidth (dB 0.1 (1) 000. (2) 001. (3) 010. Fig.29 Horizontal frequency characteristic of luminance signal (Y) dependent on ...

Page 58

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 9 LIMITING VALUES In accordance with the Absolute Maximum Rating System (IEC 134). SYMBOL PARAMETER V supply voltage; pins 14, 27, 31, 45, 61, 77 and 106 ...

Page 59

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) SYMBOL PARAMETER 2 I C-bus, SDA and SCL (pins 3 and 4) V LOW level input voltage IL V HIGH level input voltage IH I input current 3,4 I ...

Page 60

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) SYMBOL PARAMETER Horizontal PLL f nominal line frequency permissible static deviation H/ Hn Subcarrier PLL f nominal subcarrier frequency SCn f lock-in range SC Crystal oscillator; ...

Page 61

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) SYMBOL PARAMETER t VRO disable time to 3-state D t VRO enable time from 3-state E Response times to HFL flag t HFL rising edge to VRAM port HFL ...

Page 62

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) handbook, full pagewidth VOE VCLK HD3 not valid output VRO( HD3 output HFL (1) Related to VCLK (HFL). 1996 Nov 04 t VCLK ...

Page 63

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) handbook, full pagewidth clock input LLCB data input YUV, HREF, VS input CREFB control input DIR data and control output data output YUV-bus (to 3-state clock output LLCB output ...

Page 64

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) handbook, full pagewidth clock input LLC data input CVBS, CHR handbook, full pagewidth 26.8 MHz (3rd harmonic 20%) a. ...

Page 65

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 11 PROCESSING DELAYS Table 37 Processing delays of signals PORTS CVBS/CHR to YUV YUV to VRO CVBS/CHR to VRO 1996 Nov 04 DELAY IN LLC/LLCB CYCLES 216 56 in ...

Page 66

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 12 APPLICATION INFORMATION 1996 Nov 04 66 Product specification SAA7196 pagewidth full handbook, ...

Page 67

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) handbook, full pagewidth SDA SCL IICSA V DDD1 to V DDD7 0 SSD each supply has its own decoupling digital capacitor 8 CHR7 to ...

Page 68

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 12.1 Programming example Coefficients to set operation for application circuits Figs 35 and 36. Slave address byte is 40H at pin 5 connected to V (or 42H at pin ...

Page 69

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) SUBADDRESS 23 XO7 to XO0 24 HF2 to HF0, XO8, XS8 and XS9, XD8 and XD9 25 YD7 to YD0 26 YS7 to YS0 27 YO7 to YO0 28 ...

Page 70

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 13 PACKAGE OUTLINE QFP120: plastic quad flat package; 120 leads (lead length 1.95 mm); body 3.4 mm; high stand-off height pin 1 ...

Page 71

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 14 SOLDERING 14.1 Introduction There is no soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and surface mounted components are mixed ...

Page 72

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 15 DEFINITIONS Data sheet status Objective specification This data sheet contains target or goal specifications for product development. Preliminary specification This data sheet contains preliminary data; supplementary data may ...

Page 73

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 1996 Nov 04 NOTES 73 Product specification SAA7196 ...

Page 74

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 1996 Nov 04 NOTES 74 Product specification SAA7196 ...

Page 75

Philips Semiconductors Digital video decoder, Scaler and Clock generator circuit (DESCPro) 1996 Nov 04 NOTES 75 Product specification SAA7196 ...

Page 76

Philips Semiconductors – a worldwide company Argentina: see South America Australia: 34 Waterloo Road, NORTH RYDE, NSW 2113, Tel. +61 2 9805 4455, Fax. +61 2 9805 4466 Austria: Computerstr. 6, A-1101 WIEN, P.O. Box 213, Tel. + ...