PSD913212JIT ST Microelectronics, PSD913212JIT Datasheet - Page 11

PSD913212JIT

Manufacturer Part Number

PSD913212JIT

Description

Flash In-System Programmable ISP Peripherals For 8-bit MCUs

Manufacturer

ST Microelectronics

Datasheet

1.PSD913212JIT.pdf

(94 pages)

- Current page: 11 of 94

- Download datasheet (477Kb)

Preliminary Information

PSD9XX

Architectural

Overview

(cont.)

5.4 I/O Ports

The PSD9XX has 27 I/O pins divided among four ports (Port A, B, C, and D). Each

I/O pin can be individually configured for different functions. Ports A, B, C and D can

be configured as standard MCU I/O ports, PLD I/O, or latched address outputs for

microcontrollers using multiplexed address/data busses.

The JTAG pins can be enabled on Port C for In-System Programming (ISP).

Port A can also be configured as a data port for a non-multiplexed bus.

5.5 Microcontroller Bus Interface

The PSD9XX easily interfaces with most 8-bit microcontrollers that have either

multiplexed or non-multiplexed address/data busses. The device is configured to respond

to the microcontroller’s control signals, which are also used as inputs to the PLDs. Section

9.3.5 contains microcontroller interface examples.

5.6 JTAG Port

In-System Programming can be performed through the JTAG pins on Port C. This serial

interface allows complete programming of the entire PSD9XX device. A blank device can

be completely programmed. The JTAG signals (TMS, TCK, TSTAT, TERR, TDI, TDO) are

enabled on Port C when selected or when a device is blank. Table 3 indicates the JTAG

signals pin assignments.

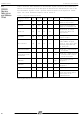

Table 3. JTAG Signals on Port C

Port C Pins

PC0

PC1

PC3

PC4

PC5

PC6

JTAG Signal

TSTAT

TERR

TMS

TDO

TCK

TDI

PSD9XX Family

7

Related parts for PSD913212JIT

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

120V - 100W DMOS AUDIO AMPLIFIER WITH MUTE/ST-BY

Manufacturer:

ST Microelectronics

Datasheet:

Part Number:

Description:

Manufacturer:

ST Microelectronics

Datasheet:

Part Number:

Description:

N-channel 55V - 0.07 Ohm - 22A StripFET Power MOSFET

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

Old PRODUCT: Not Suitable For Design-in

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

Programmable poly-phase energy calculator IC

Manufacturer:

ST Microelectronics

Datasheet:

Part Number:

Description:

High-voltage, High Current Switch

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

Single Chip Read & Write Channel

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

10A Triacs

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

20A Triacs

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

-

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

ac Line Switch

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

Video And Audio Signals Switchings For The Peri-television Plug

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

H/v Deflection With Automatic VCR Switching

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

Switch Mode Power Supply Controller

Manufacturer:

ST Microelectronics, Inc.

Datasheet:

Part Number:

Description:

Stepper Motor Driver

Manufacturer:

ST Microelectronics, Inc.

Datasheet: