AK4647VN AKM [Asahi Kasei Microsystems], AK4647VN Datasheet

AK4647VN

Related parts for AK4647VN

AK4647VN Summary of contents

Page 1

ASAHI KASEI The AK4647 features a stereo CODEC with a built-in Microphone-Amplifier and Headphone-Amplifier. Built-in PLL circuit supports an easy interface with variable systems. The AK4647 is available in a 48pin LQFP, utilizing less board space than competitive offerings. 1. ...

Page 2

ASAHI KASEI 6. Sampling Rate: • PLL Slave Mode (LRCK pin): 7.35kHz ∼ 48kHz • PLL Slave Mode (BICK pin): 7.35kHz ∼ 48kHz • PLL Slave Mode (MCKI pin): 8kHz, 11.025kHz, 12kHz, 16kHz, 22.05kHz, 24kHz, 32kHz, 44.1kHz, 48kHz • PLL ...

Page 3

... ASAHI KASEI Ordering Guide −40 ∼ +85°C AK4647VN AKD4647 Evaluation board for AK4647 Pin Layout ROUT 39 LOUT MIN RIN2/IN2− LIN2/IN2+ 45 LIN1/IN1− RIN1/IN1+ MPWR 48 MS0566-E-00 48pin LQFP (0.5mm pitch AK4647VQ 19 18 Top View ...

Page 4

ASAHI KASEI No. Pin Name I/O No Connect internal bonding. This pin should be left floating. Common Voltage Output Pin, 0.45 x AVDD 2 VCOM O Bias voltage of ADC inputs and DAC outputs. 3 AVSS ...

Page 5

ASAHI KASEI No. Pin Name I/O No Connect internal bonding. This pin should be left floating. 26 MCKI I External Master Clock Input Pin 27 MCKO O Master Clock Output Pin No Connect ...

Page 6

ASAHI KASEI Handling of Unused Pin The unused I/O pins should be processed appropriately as below. Classification Pin Name MPWR, VCOC, HPR, HPL, MUTET, ROUT, LOUT, Analog MIN, RIN2/IN2−, LIN2/IN2+, LIN1/IN1−, RIN1/IN1+ MCKO Digital MCKI (AVSS, DVSS, HVSS=0V; Note 3) ...

Page 7

ASAHI KASEI (Ta=25°C; AVDD, DVDD, HVDD=3.3V; AVSS=DVSS=HVSS=0V; fs=44.1kHz, BICK=64fs; Signal Frequency=1kHz; 16bit Data; Measurement frequency=20Hz ∼ 20kHz; unless otherwise specified) Parameter MIC Amplifier: LIN1, RIN1, LIN2, RIN2 pins; MDIF1 = MDIF2 bits = “0” (Single-ended inputs) Input MGAIN1-0 bits = ...

Page 8

ASAHI KASEI Parameter DAC Characteristics: Resolution Stereo Line Output Characteristics: DAC → LOUT, ROUT pins, ALC=OFF, IVOL=0dB, DVOL=0dB, LOVL bit = “0”, R Output Voltage (Note 13) LOVL bit = “0” LOVL bit = “1” S/(N+D) (−3dBFS) S/N (A-weighted) Interchannel ...

Page 9

ASAHI KASEI Parameter Mono Input: MIN pin (External Input Resistance=20kΩ) Maximum Input Voltage (Note 17) Gain Note 18(Note 18) MIN LOUT/ROUT LOVL bit = “0” LOVL bit = “1” MIN HPL/HPR HPG bit = “0” HPG bit = “1” Power ...

Page 10

ASAHI KASEI (Ta=25°C; AVDD, DVDD=2.6 ∼ 3.6V; HVDD=2.6 ∼ 5.25V; fs=44.1kHz; DEM=OFF; FIL1=FIL3=EQ=OFF) Parameter ADC Digital Filter (Decimation LPF): ±0.16dB Passband (Note 22) −0.66dB −1.1dB −6.9dB Stopband Passband Ripple Stopband Attenuation Group Delay (Note 23) Group Delay Distortion ADC Digital ...

Page 11

ASAHI KASEI (Ta=25°C; AVDD, DVDD=2.6 ∼ 3.6V; HVDD=2.6 ∼ 5.25V) Parameter High-Level Input Voltage Low-Level Input Voltage High-Level Output Voltage Low-Level Output Voltage (Except SDA pin: Iout=200μA) (SDA pin: Iout=3mA) Input Leakage Current (Ta=25°C; AVDD, DVDD=2.6 ∼ 3.6V; HVDD=2.6 ∼ ...

Page 12

ASAHI KASEI Parameter PLL Slave Mode (PLL Reference Clock = LRCK pin) LRCK Input Timing Frequency Duty BICK Input Timing Period Pulse Width Low Pulse Width High PLL Slave Mode (PLL Reference Clock = BICK pin) LRCK Input Timing Frequency ...

Page 13

ASAHI KASEI Parameter Control Interface Timing (3-wire Serial mode) CCLK Period CCLK Pulse Width Low Pulse Width High CDTI Setup Time CDTI Hold Time CSN “H” Time CSN “↓” to CCLK “↑” CCLK “↑” to CSN “↑” 2 Control Interface ...

Page 14

ASAHI KASEI Timing Diagram MCKI tCLKH LRCK MCKO Figure 3. Clock Timing (PLL Master mode) LRCK tBLR BICK SDTO SDTI Figure 4. Audio Interface Timing (PLL Master mode) MS0566-E-00 1/fCLK tCLKL 1/fs tLRCKH tLRCKL Duty = tLRCKH ...

Page 15

ASAHI KASEI MCKI tCLKH LRCK tLRCKH BICK tBCKH MCKO Figure 5. Clock Timing (PLL Slave mode; PLL Reference Clock = MCKI pin) MCKI LRCK BICK MS0566-E-00 1/fCLK tCLKL 1/fs tLRCKL Duty = tLRCKH 100 = tLRCKL x ...

Page 16

ASAHI KASEI LRCK tBLR BICK tLRD SDTO SDTI Figure 7. Audio Interface Timing (PLL/EXT Slave mode) CSN CCLK CDTI CSN CCLK CDTI D2 MS0566-E-00 tLRB tBSD MSB tSDS tSDH tCSS tCCKL tCCKH tCDS C1 C0 Figure 8. WRITE Command Input ...

Page 17

ASAHI KASEI SDA tBUF tLOW tR SCL tHD:STA Stop Start PMADL bit or PMADR bit SDTO Timing PDN MS0566-E-00 tHIGH tF tHD:DAT tSU:DAT tSU:STA Start 2 Figure 10 Bus Mode tPDV Figure 11. Power Down & Reset Timing ...

Page 18

ASAHI KASEI System Clock There are the following four clock modes to interface with external devices (see Table 1 and Table 2). Mode PLL Master Mode PLL Slave Mode 1 (PLL Reference Clock: MCKI pin) PLL Slave Mode 2 (PLL ...

Page 19

ASAHI KASEI PLL Mode When PMPLL bit is “1”, a fully integrated analog phase locked loop (PLL) generates a clock that is selected by the PLL3-0 and FS3-0 bits. The PLL lock time is shown in Table 4, whenever the ...

Page 20

ASAHI KASEI PLL Unlock State 1) PLL Master Mode (PMPLL bit = “1”, M/S bit = “1”) In this mode, LRCK and BICK pins go to “L” and irregular frequency clock is output from MCKO pins at MCKO bit is ...

Page 21

ASAHI KASEI PLL Master Mode (PMPLL bit = “1”, M/S bit = “1”) When an external clock (11.2896MHz, 12MHz, 12.288MHz, 13.5MHz, 24MHz or 27MHz) is input to MCKI pin, the MCKO, BICK and LRCK clocks are generated by an internal ...

Page 22

ASAHI KASEI PLL Slave Mode (PMPLL bit = “1”, M/S bit = “0”) A reference clock of PLL is selected among the input clocks to MCKI, BICK or LRCK pin. The required clock to the AK4647 is generated by an ...

Page 23

ASAHI KASEI b) PLL reference clock: BICK or LRCK pin Sampling frequency corresponds to 7.35kHz to 48kHz by changing FS3-0 bits (see Table 6). AK4647 Figure 15. PLL Slave Mode 2 (PLL Reference Clock: BICK pin) AK4647 Figure 16. PLL ...

Page 24

ASAHI KASEI EXT Slave Mode (PMPLL bit = “0”, M/S bit = “0”) When PMPLL bit is “0”, the AK4647 becomes EXT mode. Master clock is input from MCKI pin, the internal PLL circuit is not operated. This mode is ...

Page 25

ASAHI KASEI System Reset Upon power-up, the AK4647 should be reset by bringing the PDN pin = “L”. This ensures that all internal registers reset to their initial values. The ADC enters an initialization cycle that starts when the PMADL ...

Page 26

ASAHI KASEI LRCK BICK(32fs SDTO( SDTI( BICK(64fs SDTO( SDTI(i) 15:MSB, 0:LSB LRCK BICK(32fs) SDTO( ...

Page 27

ASAHI KASEI Digital High Pass Filter The ADC has a digital high pass filter for DC offset cancellation. The cut-off frequency of the HPF is 0.9Hz (@fs=44.1kHz) and scales with sampling rate (fs). When PMADL bit = “1” or PMADR ...

Page 28

ASAHI KASEI AK4647 LIN1/IN1− pin RIN1/IN1+ pin RIN2/IN2− pin LIN2/IN2+ pin 1k 1k Figure 22. Connection Example for Full-differential Mic Input (MDIF1/2 bits = “1”) <Input Selector Setting Example> In case that IN1+/− pins are used as full-differential mic input ...

Page 29

ASAHI KASEI MIC Gain Amplifier The AK4647 has a gain amplifier for microphone input. The gain of MIC-Amp is selected by the MGAIN1-0 bits (see Table 18). The typical input impedance is 60kΩ(typ)@MGAIN1-0 bits = “00” or 30kΩ(typ)@MGAIN1-0 bits = ...

Page 30

ASAHI KASEI Digital EQ/HPF/LPF The AK4647 performs wind-noise reduction filter, stereo separation emphasis, gain compensation and ALC (Automatic Level Control) by digital domain for A/D converted data (Figure 24). FIL1, FIL3 and EQ blocks are IIR filters of 1 order. ...

Page 31

ASAHI KASEI [Filter Coefficient Setting] 1) When FIL1 and FIL2 are set to “HPF” fs: Sampling frequency fc: Cut-off frequency f: Input signal frequency K: Filter gain [dB] (Filter gain of should be set to 0dB.) Register setting FIL1: F1AS ...

Page 32

ASAHI KASEI 3) EQ fs: Sampling frequency fc : Pole frequency Zero-point frequency 2 f: Input signal frequency K: Filter gain [dB] (Maximum +12dB) Register setting EQA[15:0] bits =A, EQB[13:0] bits =B, EQC[15:0] bits =C (MSB=EQA15, EQB13, ...

Page 33

ASAHI KASEI ALC Operation The ALC (Automatic Level Control) is done by ALC block when ALC bit is “1”. When only DAC is powered-up, ALC circuit operates at playback path. When only ADC is powered-up or both ADC and DAC ...

Page 34

ASAHI KASEI 2. ALC Recovery Operation The ALC recovery operation waits for the WTM1-0 bits (Table 26 set after completing the ALC limiter operation. If the input signal does not exceed “ALC recovery waiting counter reset level” (Table ...

Page 35

ASAHI KASEI 3. Example of ALC Operation Table 29 shows the examples of the ALC setting for mic recording. Register Name Comment LMTH1-0 Limiter detection Level ZELMN Limiter zero crossing detection ZTM1-0 Zero crossing timeout period Recovery waiting period WTM1-0 ...

Page 36

ASAHI KASEI Input Digital Volume (Manual Mode) The input digital volume becomes a manual mode when ALC bit is “0”. This mode is used in the case shown below. 1. After exiting reset state, set-up the registers for the ALC ...

Page 37

ASAHI KASEI When writing to the IVL7-0 and IVR7-0 bits continuouslly, the control register should be written by an interval more than zero crossing timeout. If not, IVL and IVR are not changed since zero crossing counter is reset at ...

Page 38

ASAHI KASEI De-emphasis Filter The AK4647 includes the digital de-emphasis filter (tc = 50/15μs) by IIR filter. Setting the DEM1-0 bits enables the de-emphasis filter (Table 31). DEM1 Bass Boost Function The BST1-0 bits control the ...

Page 39

ASAHI KASEI Digital Output Volume The AK4647 has a digital output volume (256 levels, 0.5dB step, Mute). The volume can be set by the DVL7-0 and DVR7-0 bits. The volume is included in front of a DAC block. The input ...

Page 40

ASAHI KASEI Soft Mute Soft mute operation is performed in the digital domain. When the SMUTE bit goes to “1”, the output signal is attenuated by −∞ (“0”) during the cycle set by the DVTM bit. When the SMUTE bit ...

Page 41

ASAHI KASEI Analog Mixing : Mono Input When the PMBP bit is set to “1”, the mono input is powered-up. When the BEEPH bit is set to “1”, the input signal from the MIN pin is output to Headphone-Amp. When ...

Page 42

ASAHI KASEI Stereo Line Output (LOUT/ROUT pins) When DACL bit is “1”, Lch/Rch signal of DAC is output from the LOUT/ROUT pins which is single-ended. When DACL bit is “0”, output signal is muted and LOUT/ROUT pins output VCOM voltage. ...

Page 43

ASAHI KASEI [Stereo Line Output Control Sequence (in case of using Pop Reduction Circuit ...

Page 44

ASAHI KASEI Headphone Output Power supply voltage for the Headphone-Amp is supplied from the HVDD pin and centered on the HVDD/2 voltage. The load resistance and output voltage are specified by HVDD voltage. HPG bit selects the output voltage (see ...

Page 45

ASAHI KASEI <External Circuit of Headphone-Amp > When BOOST=OFF, the cut-off frequency (fc) of Headphone-Amp depends on the external resistor and capacitor. This fc can be shifted to lower frequency by using bass boost function. Table 40 shows the cut ...

Page 46

ASAHI KASEI Serial Control Interface (1) 3-wire Serial Control Mode (I2C pin = “L”) Internal registers may be written by using the 3-wire µP interface pins (CSN, CCLK and CDTI). The data on this interface consists of a 2-bit Chip ...

Page 47

ASAHI KASEI 2 (2) I C-bus Control Mode (I2C pin = “H”) 2 The AK4647 supports the fast-mode I to (DVDD+0.3)V or less voltage. (2)-1. WRITE Operations Figure 36 shows the data transfer sequence for the I HIGH to LOW ...

Page 48

ASAHI KASEI (2)-2. READ Operations Set the R/W bit = “1” for the READ operation of the AK4647. After transmission of data, the master can read the next address’s data by generating an acknowledge instead of terminating the write cycle ...

Page 49

ASAHI KASEI SDA SCL S start condition DATA OUTPUT BY TRANSMITTER DATA OUTPUT BY RECEIVER SCL FROM MASTER S START CONDITION SDA SCL MS0566-E-00 Figure 42. START and STOP Conditions Figure 43. Acknowledge on the I C-Bus ...

Page 50

ASAHI KASEI Register Map Addr Register Name 00H Power Management 1 01H Power Management 2 02H Signal Select 1 03H Signal Select 2 LOVL 04H Mode Control 1 PLL3 05H Mode Control 2 PS1 06H Timer Select DVTM 07H ALC ...

Page 51

ASAHI KASEI Register Definitions Addr Register Name D7 00H Power Management 1 0 Default 0 PMADL: MIC-Amp Lch and ADC Lch Power Management 0: Power-down (Default) 1: Power-up When the PMADL or PMADR bit is changed from “0” to “1”, ...

Page 52

ASAHI KASEI Addr Register Name D7 01H Power Management 2 0 Default 0 PMPLL: PLL Power Management 0: EXT Mode and Power-Down (Default) 1: PLL Mode and Power-up MCKO: Master Clock Output Enable 0: Disable: MCKO pin = “L” (Default) ...

Page 53

ASAHI KASEI Addr Register Name 03H Signal Select 2 LOVL Default BEEPL: Switch Control from MIN pin to Stereo Line Output 0: OFF (Default When PMLO bit is “1”, BEEPL bit is enabled. When PMLO bit is “0”, ...

Page 54

ASAHI KASEI Addr Register Name 06H Timer Select DVTM Default WTM1-0: ALC Recovery Waiting Period (see Table 26.) Default: “00” (128/fs) ZTM1-0: ALC Limiter/Recovery Operation Zero Crossing Timeout Period (see Table 25.) Default: “00” (128/fs) DVTM: Digital Volume Transition Time ...

Page 55

ASAHI KASEI Addr Register Name 09H Lch Input Volume Control 0CH Rch Input Volume Control Default IVL7-0, IVR7-0: Input Digital Volume; 0.375dB step, 242 Level (see Table 30.) Default: “E1H” (+30.0dB) Addr Register Name 0AH Lch Digital Volume Control DVL7 ...

Page 56

ASAHI KASEI Addr Register Name 0FH Mode Control 4 Default DACH: Switch Control from DAC to Headphone-Amp 0: OFF (Default BEEPH: Switch Control from MIN pin to Headphone-Amp 0: OFF (Default HPM: Headphone-Amp Mono Output Select ...

Page 57

ASAHI KASEI Addr Register Name 11H Digital Filter Select Default GN1-0: Gain Select at GAIN block (See Table 21) Default: “00” FIL3: FIL3 (Stereo Separation Emphasis Filter) Coefficient Setting Enable 0: Disable (Default) 1: Enable When FIL3 bit is “1”, ...

Page 58

ASAHI KASEI Addr Register Name 12H FIL3 Co-efficient 0 13H FIL3 Co-efficient 1 14H FIL3 Co-efficient 2 15H FIL3 Co-efficient 3 16H EQ Co-efficient 0 EQA7 17H EQ Co-efficient 1 EQA15 18H EQ Co-efficient 2 19H EQ Co-efficient 3 1AH ...

Page 59

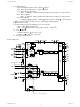

ASAHI KASEI Figure 45 and shows the system connection diagram for the AK4647. An evaluation board [AKD4647] is available which demonstrates the optimum layout, power supply arrangements and measurement results. 10u Power Supply 2.6 ∼ 3.6V 1u 200 1u Line ...

Page 60

ASAHI KASEI 10u Power Supply 2.6 ∼ 3.6V 1u 200 1u Line Out 1u 200 Mono In Line In Notes: - AVSS, DVSS and HVSS of the AK4647 should be distributed separately from the ground of external controllers. - All ...

Page 61

ASAHI KASEI 1. Grounding and Power Supply Decoupling The AK4647 requires careful attention to power supply and grounding arrangements. AVDD, DVDD and HVDD are usually supplied from the system’s analog supply. If AVDD, DVDD and HVDD are supplied separately, the ...

Page 62

ASAHI KASEI Clock Set up When ADC or DAC is powered-up, the clocks must be supplied. 1. PLL Master Mode. Power Supply (1) PDN pin (2) (3) PMVCM bit (Addr:00H, D6) (4) MCKO bit (Addr:01H, D1) PMPLL bit (Addr:01H, D0) ...

Page 63

ASAHI KASEI 2. PLL Slave Mode (LRCK or BICK pin) Power Supply (1) PDN pin (2) (3) PMVCM bit (Addr:00H, D6) PMPLL bit (Addr:01H, D0) LRCK pin BICK pin Internal Clock <Example> (1) After Power Up: PDN pin “L” “L” ...

Page 64

ASAHI KASEI 3. PLL Slave Mode (MCKI pin) Power Supply (1) PDN pin (2) (3) PMVCM bit (Addr:00H, D6) (4) MCKO bit (Addr:01H, D1) PMPLL bit (Addr:01H, D0) (5) MCKI pin MCKO pin BICK pin LRCK pin <Example> (1) After ...

Page 65

ASAHI KASEI 4. EXT Slave Mode Power Supply (1) PDN pin (2) (3) PMVCM bit (Addr:00H, D6) (4) MCKI pin (4) LRCK pin BICK pin <Example> (1) After Power Up: PDN pin “L” “L” time of 150ns or more is ...

Page 66

ASAHI KASEI MIC Input Recording (Stereo) FS3-0 bits 0,000 (Addr:05H, D5&D2-0) (1) MIC Control 001 (Addr:02H, D2-0) (2) ALC Control 1 00H (Addr:06H) (3) ALC Control 2 E1H (Addr:08H) (4) ALC Control 3 00H (Addr:0BH) (5) ALC Control 4 07H ...

Page 67

ASAHI KASEI Headphone-amp Output FS3-0 bits 0,000 (Addr:05H, D5&D2-0) (1) DACH bit (Addr:0FH, D0) BST1-0 bits 00 (Addr:0EH, D3-2) (3) IVL/R7-0 bits E1H (Addr:09H&0CH, D7-0) DVL/R7-0 bits 18H (Addr:0AH&0DH, D7-0) PMDAC bit (Addr:00H, D2) PMBP bit (Addr:00H, D5) PMHPL/R bits ...

Page 68

ASAHI KASEI Stereo Line Output FS3-0 bits 0,000 (Addr:05H, D5&D2-0) (1) DACL bit (2) (Addr:02H, D4) IVL/R7-0 bits E1H (Addr:09H&0CH, D7-0) (3) DVL/R7-0 bits 18H (Addr:0AH&0DH, D7-0) (4) LOPS bit (Addr:03H, D6) (5) PMDAC bit (Addr:00H, D2) PMBP bit (Addr:00H, ...

Page 69

ASAHI KASEI Stop of Clock Master clock can be stopped when ADC and DAC are not used. 1. PLL Master Mode (1) PMPLL bit (Addr:01H, D0) (2) MCKO bit "1" or "0" (Addr:01H, D1) (3) External MCKI Input <Example> (1) ...

Page 70

ASAHI KASEI 3. PLL Slave (MCKI pin) (1) PMPLL bit (Addr:01H, D0) (1) MCKO bit (Addr:01H, D1) (2) External MCKI Input <Example> (1) Power down PLL: PMPLL bit = “1” → “0” Stop MCKO output: MCKO bit = “1” → ...

Page 71

ASAHI KASEI 48pin LQFP(Unit:mm) 9.0 ± 0.2 7 0.22 ± 0.08 0.5 0.10 Material & Lead finish Package molding compound: Lead frame material: Lead frame surface treatment: MS0566-E-00 PACKAGE 1.70Max 25 1.40 ± 0. ...

Page 72

ASAHI KASEI Date (YY/MM/DD) Revision Reason 06/11/10 00 First Edition • These products and their specifications are subject to change without notice. Before considering any use or application, consult the Asahi Kasei Microsystems Co., Ltd. (AKM) sales office or authorized ...