NBSG16MMNR2G ON Semiconductor, NBSG16MMNR2G Datasheet - Page 2

NBSG16MMNR2G

Manufacturer Part Number

NBSG16MMNR2G

Description

IC RCVR/DRVR CML 2.5/3.3V 16-QFN

Manufacturer

ON Semiconductor

Type

Transceiverr

Datasheet

1.NBSG16MMNR2G.pdf

(11 pages)

Specifications of NBSG16MMNR2G

Applications

Instrumentation

Mounting Type

Surface Mount

Package / Case

16-TFQFN Exposed Pad

Logic Family

NBSG

Logic Type

Receiver and Driver Translator Buffer

Supply Voltage (max)

3.465 V, - 3.465 V

Supply Voltage (min)

2.375 V, - 2.375 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Data Rate

10000 Mbps

Minimum Operating Temperature

- 40 C

Supply Current

51 mA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Á Á Á

Á Á Á

1. The NC pins are electrically connected to the die and MUST be left open.

2. CML outputs require 50 W receiver termination resistor to V

3. In the differential configuration when the input termination pin (V

Table 1. PIN DESCRIPTION

Pin

10

11

12

13

14

15

16

1

2

3

4

5

6

7

8

9

−

is applied then the device will be susceptible to self−oscillation.

Á Á Á

Á Á Á

Name

V

V

V

V

V

V

V

V

V

V

V

NC

EP

D

D

Q

Q

TD

TD

CC

EE

EE

CC

CC

EE

EE

BB

CC

LVDS, CML, ECL, LVTTL,

LVDS, CML, ECL, LVTTL,

LVCMOS Input

LVCMOS Input

CML Output

CML Output

I/O

−

−

−

−

−

−

−

−

−

−

−

−

−

VTD

VTD

Á Á Á Á Á Á Á Á Á Á Á Á Á Á Á Á Á Á Á Á Á Á Á

Á Á Á Á Á Á Á Á Á Á Á Á Á Á Á Á Á Á Á Á Á Á Á

D

D

Internal 50 W Termination Pin. See Table 2. (Note 3)

Inverted Differential Input (Note 3)

Noninverted Differential Input. (Note 3)

Internal 50 W Termination Pin. See Table 2. (Note 3)

Positive Supply Voltage. All V

antee proper operation.

No Connect (Note 1)

Negative Supply Voltage. All V

antee proper operation.

Negative Supply Voltage. All V

antee proper operation.

Positive Supply Voltage. All V

antee proper operation.

Noninverted CML Differential Output with Internal 50 W Source Termination Resistor. (Note 2)

Inverted CML Differential Output with Internal 50 W Source Termination Resistor. (Note 2)

Positive Supply Voltage. All V

antee proper operation.

Negative Supply Voltage. All V

antee proper operation.

Negative Supply Voltage. All V

antee proper operation.

Internally Generated ECL Reference Output Voltage

Positive Supply Voltage. All V

antee proper operation.

The Exposed Pad (EP) and the QFN−16 package bottom is thermally connected to the die

for improved heat transfer out of package. The exposed pad must be attached to a heat−

sinking conduit. The pad is not electrically connected to the die but may be electrically and

thermally connected to V

1

2

3

4

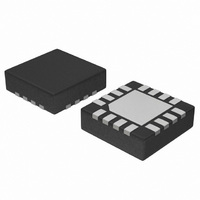

Figure 1. QFN−16 Pinout (Top View)

V

V

16

CC

CC

5

http://onsemi.com

V

NBSG16M

15

NC V

BB

6

CC

V

14

for proper operation.

EE

TD

7

EE

, V

2

EE

TD

V

V

13

8

on the PC board.

EE

EE

) are connected to a common termination voltage, and if no signal

CC

CC

CC

CC

EE

EE

EE

EE

pins must be externally connected to Power Supply to guar-

pins must be externally connected to Power Supply to guar-

pins must be externally connected to Power Supply to guar-

pins must be externally connected to Power Supply to guar-

pins must be externally connected to Power Supply to guar-

pins must be externally connected to Power Supply to guar-

pins must be externally connected to Power Supply to guar-

pins must be externally connected to Power Supply to guar-

12

11

10

9

V

Q

Q

V

Description

CC

CC

Exposed Pad (EP)