NBSG53ABAEVB ON Semiconductor, NBSG53ABAEVB Datasheet - Page 10

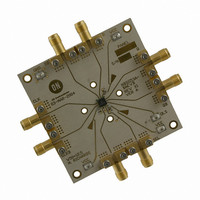

NBSG53ABAEVB

Manufacturer Part Number

NBSG53ABAEVB

Description

BOARD EVAL BBG NBSG53ABA

Manufacturer

ON Semiconductor

Datasheet

1.NBSG53AMNR2G.pdf

(18 pages)

Specifications of NBSG53ABAEVB

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

For Use With/related Products

NBSG53A

Other names

NBSG53ABAEVB

NBSG53ABAEVBOS

NBSG53ABAEVBOS

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit

30. Measured using a 500 mV source, 50% duty cycle clock source. Repetitive 1010 input data pattern. All outputs loaded with 50 W to

31. See Figure 14. t

32. V

33. See Figure 10. Duty Cycle % vs. Frequency.

34. For all OLS Configuration.

**When an output level of 400 mV is desired and V

***The device packaged in FCBGA−16 have maximum ambient temperature specification of 70°C and devices packaged in QFN−16 have

Table 11. AC CHARACTERISTICS for QFN−16

V

Symbol

maximum ambient temperature specification of 85°C.

f

t

t

t

t

V

t

t

t

t

t

max

PLH

PHL

SKEW

JITTER

r

f

s

h

rr

CC

INPP

V

CC

INPP

,

= 0 V; V

board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared

operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit

values are applied individually under normal operating conditions and not valid simultaneously.

− 2.0 V. Input edge rates is 40 ps (20% − 80%).

(MAX) cannot exceed V

Maximum Frequency

(See Figures 4, 6, 8, 10, and 11)

(See Figures 5, 7, 9, 10, and 11)

(Note 30)

Propagation Delay to Output Differential

Duty Cycle Skew (Notes 31 and 33) DFF

RMS Random Clock Jitter

(See Figures 4 and 6) (Note 30)

Peak−to−Peak Data Dependent Jitter

Input Voltage Swing/Sensitivity

(Differential Configuration) (Note 32)

Output Rise/Fall Times (20% − 80%)

@ 1 GHz

Setup Time

Hold Time

Reset Recovery

(Note 34)

EE

= −3.465 V to −2.375 V or V

(OLS = V

SKEW

Characteristic

= |t

CC

PLH

− 0.8 V, OLS = FLOAT)

− t

(OLS = V

CC

PHL

− V

| for a nominal 50% differential clock input waveform.

R→Q, Q D

**(OLS = V

EE

(OLS = V

f

CLK→Q, Q

SEL→Q, Q

in

f

CC

DFF, DIV/2

in

(Applicable only when V

v 8 GHz

= 8 Gb/s

D→CLK

D→CLK

− 0.4 V)

CC

DIV/2

Q, Q

= 2.375 V to 3.465 V; V

DFF

DFF

IN

CC

EE

CC

/2

)

)

− V

Min

150

160

215

195

EE

75

28

15

25

20

30

25

40

http://onsemi.com

> 3.0 V, a 2 kW resistor should be connected from OLS to V

−40°C

TBD

Typ

215

190

280

270

0.5

10

40

40

35

35

14

12

8

5

9

CC

10

− V

EE

2600

EE

Max

285

280

375

345

20

65

65

65

65

= 0 V

1

< 2600 mV).

Min

150

160

215

195

75

28

15

25

20

30

25

40

25°C

TBD

Typ

215

190

280

270

0.5

10

40

40

35

35

10

12

8

5

7

2600

Max

285

280

375

345

20

65

65

65

65

1

Min

150

160

215

195

75

28

15

25

20

30

25

40

85°C

TBD

Typ

215

190

280

270

0.5

10

40

40

35

35

13

10

8

5

0

EE

.

2600

Max

285

280

375

345

20

65

65

65

65

1

GHz

Unit

mV

ps

ps

ps

ps

ps

ps

ps