NBSG111BAEVB ON Semiconductor, NBSG111BAEVB Datasheet - Page 9

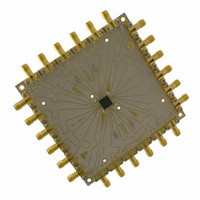

NBSG111BAEVB

Manufacturer Part Number

NBSG111BAEVB

Description

BOARD EVALUATION BBG NBSG111BA

Manufacturer

ON Semiconductor

Specifications of NBSG111BAEVB

Main Purpose

Clock/Data Driver

Utilized Ic / Part

NBSG111

Primary Attributes

W/RSECL Outputs

Technology Type

Evaluation Board

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

For Use With/related Products

NBSG111

Other names

NBSG111BAEVB

NBSG111BAEVBOS

NBSG111BAEVBOS

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit

18. Measured using a 500 mV source, 50% duty cycle clock source. All outputs loaded with 50 W to V

19. t

20. Within−Device skew is measured between outputs under identical transitions and conditions on any one device.

21. Device−to−Device skew for identical transitions at identical V

22. V

23. Additive RMS jitter with 50% duty cycle clock signal at 5 GHz.

24. Additive Peak−to−Peak jitter with input NRZ data at PRBS 2

Table 9. AC CHARACTERISTICS

Symbol

V

t

t

t

t

t

t

V

t

t

PLH

PHL

SKEW

S

H

JITTER

r

f

OUTPP

INPP

(20% − 80%).

SKEW

INPP

,

board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared

operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit

values are applied individually under normal operating conditions and not valid simultaneously.

(MAX) cannot exceed V

= |t

Output Voltage Amplitude

(See Figure 3) (Note 18)

Propagation Delay to Output Differential

Output Enable

Clock Select

Duty Cycle Skew (Note 19)

Within−Device Skew (Note 20)

Device−to−Device Skew (Note 21)

Setup Time to CLK (EN to Selected CLK0:1)

Hold Time (EN to Selected CLK0:1)

RMS Random Clock Jitter(Figure 3)

(Note 23)

Peak−to−Peak Data Dependent Jitter

(Note 24)

Input Voltage Swing/Sensitivity

(Differential Configuration) (Note 22)

Output Rise/Fall Times (20% − 80%) @ 1 GHz

PLH

− t

PHL

| for a nominal 50% differential clock input waveform (Figure 4).

550

450

350

250

150

Characteristic

Figure 3. Output Voltage Amplitude (V

CC

1

Input Frequency (f

− V

RMS JITTER (ps)

EE

V

Q AMP (mV)

CC

(applicable only when V

= 0 V; V

2

f

in

f

f

f

in

in

in

= 5.5 GHz

EE

= 5 Gb/s

< 3 GHz

= 5 GHz

INPUT FREQUENCY (GHz)

= −3.465 V to −2.375 V or V

Q, Q

http://onsemi.com

in

) at Ambient Temperature (Typical)

3

31

CC

2.5 V

−1 at 5 Gb/s.

Min

305

180

250

430

400

110

110

75

40

CC

levels.

3.3 V

9

−V

−40°C

EE

Typ

420

250

300

550

450

0.5

15

70

70

60

2

5

t 2600 mV).

4

OUTPP

2600

Max

350

700

500

2.0

15

20

85

80

CC

) / RMS Jitter vs.

= 2.375 V to 3.465 V; V

Min

305

150

250

430

400

110

110

75

40

5

25°C

Typ

420

220

300

550

450

0.5

15

70

70

14

60

2

5

2600

Max

350

700

500

2.0

CC

15

20

85

80

6

− 1.5 V. Input edge rates 40 ps

10.0

9.0

8.0

7.0

6.0

5.0

4.0

3.0

2.0

1.0

0.0

Min

305

100

250

430

400

115

115

EE =

75

40

0 V

70°C

Typ

420

200

300

600

480

0.5

15

80

80

60

2

5

2600

Max

350

750

550

2.0

15

20

85

80

Unit

mV

mV

ps

ps

ps

ps

ps

ps