LP5952TL-1.5/NOPB National Semiconductor, LP5952TL-1.5/NOPB Datasheet - Page 7

LP5952TL-1.5/NOPB

Manufacturer Part Number

LP5952TL-1.5/NOPB

Description

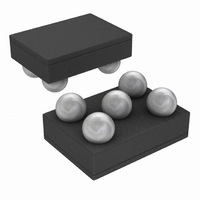

IC REG LDO 1.5V 350MA 5MICROSMD

Manufacturer

National Semiconductor

Series

PowerWise®r

Datasheet

1.LP5952TL-1.2EV.pdf

(16 pages)

Specifications of LP5952TL-1.5/NOPB

Regulator Topology

Positive Fixed

Voltage - Output

1.5V

Voltage - Input

Up to 4.5V

Voltage - Dropout (typical)

0.088V @ 350mA

Number Of Regulators

1

Current - Output

350mA

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

5-MicroSMD

For Use With

LP5952TL-1.5EV - BOARD EVALUATION LP5952TL-1.5

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Current - Limit (min)

-

Other names

LP5952TL-1.5TR

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LP5952TL-1.5/NOPB

Manufacturer:

Texas Instruments

Quantity:

10 000

Transient Characteristics

Input and Output Capacitors, Recommended Specification

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under which operation

of the device is guaranteed. Operating Ratings do not imply guaranteed performance limits. For guaranteed performance limits and associated test conditions,

see the Electrical Characteristics tables.

Note 2: All voltages are with respect to the potential at the GND pin.

Note 3: Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at T

= 145°C (typ.).

Note 4: For detailed soldering specifications and information, please refer to National Semiconductor Application Note 1112: Micro SMD Wafer Level Chip Scale

Package (AN-1112) and Application Note 1187: Leadless Leadframe Package (LLP) (AN-1187).

Note 5: The Human body model is a 100pF capacitor discharged through a 1.5kΩ resistor into each pin. The machine model is a 200pF capacitor discharged

directly into each pin. (MIL-STD-883 3015.7)

Note 6: In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be

derated. Maximum ambient temperature (T

dissipation of the device in the application (P

following equation: T

Note 7: Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists,

special attention must be paid to thermal dissipation issues in board design.

Note 8: Min and Max limits are guaranteed by design, test, or statistical analysis. Typical (Typ) numbers are not guaranteed, but do represent the most likely

norm. Unless otherwise specified, conditions for Typ specifications are: V

C.

Note 9: Dropout voltage is defined as the input to output voltage differential at which the output voltage falls to 100mV below the nominal output voltage.

Note 10: This specification does not apply if the battery voltage V

Note 11: V

Note 12: The capacitor tolerance should be 30% or better over temperature. The full operating conditions for the application should be considered when selecting

a suitable capacitor to ensure that the minimum value of capacitance is always met. Recommended capacitor type is X7R. However, dependent on application,

X5R, Y5V, and Z5U can also be used. The shown minimum limit represents real minimum capacitance, including all tolerances and must be maintained over

temperature and dc bias voltage (See capacitor section in Applications Hints)

ΔV

ΔV

ΔV

T

C

C

STARTUP

OUT

VIN

OUT

OUT

OUT

Symbol

Symbol

OUT(NOM)

is the stated output voltage option

A-MAX

Dynamic Line Transient

Response V

Dynamic Line Transient

Response V

Dynamic Load Transient

Response

Startup Time

Output Capacitance

Input Capacitance at V

= T

J-MAX-OP

Parameter

Parameter

IN

BATT

– (θ

JA

A-MAX

× P

D-MAX

D-MAX

) is dependent on the maximum operating junction temperature (T

), and the junction-to ambient thermal resistance of the part/package in the application (θ

IN

).

V

V

V

V

Pulsed load 0 ...300mA, di/dt = 300mA/

1µs

micro SMD package

Pulsed load 0 ...300mA, di/dt = 300mA/

1µs

LLP-6 package

EN to 0.95 * V

Capacitance (Note 12)

ESR

Capacitance (Note 12), not needed in typ

post regulation application,

see Figure 1

ESR

BATT

IN

OUT(NOM)

BATT

OUT(NOM)

= V

needs to be decreased below the minimum operating limit of 2.5V during this test.

= V

IN

OUT(NOM)

= V

OUT(NOM)

+ 0.9V; tr, tf = 10µs

+ 2.1V; tr, tf = 10µs

7

OUT(NOM)

OUT

Conditions

Conditions

+ 0.3V to

+ 1.5V to

+ 1.0V, V

BATT

= V

OUT(NOM)

+ 1.5V or 2.5V, whichever is higher, T

J-MAX-OP

Nom

Typ

-35/

±15

±15

+15

2.2

±1

70

1

J

= 125°C), the maximum power

= 165°C (typ.) and disengages at T

0.47

Min

Min

1.5

3

3

Limit

Limit

JA

Max

Max

), as given by the

150

300

300

10

www.national.com

Units

Units

mV

mV

mV

mV

mΩ

mΩ

A

µF

µF

µs

= 25°

J