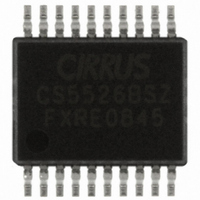

CS5526-BSZ Cirrus Logic Inc, CS5526-BSZ Datasheet - Page 16

CS5526-BSZ

Manufacturer Part Number

CS5526-BSZ

Description

IC ADC 20BIT W/4BIT LATCH 20SSOP

Manufacturer

Cirrus Logic Inc

Datasheet

1.CS5526-BSZ.pdf

(30 pages)

Specifications of CS5526-BSZ

Number Of Converters

1

Package / Case

20-SSOP

Number Of Bits

20

Data Interface

Serial

Power Dissipation (max)

12.7mW

Voltage Supply Source

Analog and Digital

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Number Of Adc Inputs

1

Architecture

Delta-Sigma

Conversion Rate

3.76 SPs to 616 SPs

Resolution

20 bit

Input Type

Voltage

Interface Type

Serial (3-Wire)

Voltage Reference

2.5 V

Supply Voltage (max)

5 V

Supply Voltage (min)

25 mV

Maximum Power Dissipation

500 mW

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Input Voltage

25 mV to 5 V

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1014 - EVAL BOARD FOR CS5526

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

598-1108-5

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CS5526-BSZ

Manufacturer:

CIRRUS

Quantity:

1 000

Part Number:

CS5526-BSZ

Manufacturer:

CIRRUS

Quantity:

20 000

Charge Pump Drive

The CPD (Charge Pump Drive) pin of the convert-

ers can be used with external components (shown

in Figure 1) to develop an appropriate negative bias

voltage for the NBV pin. When CPD is used to gen-

erate the NBV, the NBV voltage is regulated with

an internal regulator loop referenced to VA+.

Therefore, any change on VA+ results in a propor-

tional change on NBV. With VA+ = 5 V, NBV’s

regulation is set proportional to VA+ at approxi-

mately -2.1 V.

Figure 3 illustrates a means of supplying NBV volt-

age from a -5 V supply. For ground based signals

with the instrumentation amplifier engaged (when

in the 25mV, 55mV, or 100mV ranges), the voltage

on the NBV pin should at no time be less negative

than -1.8 V or more negative than -2.5 V. To pre-

vent excessive voltage stress to the chip the NBV

voltage should not be more negative than -3.0 V.

The components in Figure 1 are the preferred com-

ponents for the CPD filter. However, smaller ca-

pacitors can be used with acceptable results. The

10

safety requirements prohibit the use of electrolytic

capacitors. In this case, two 0.47

itors in parallel can be used.

The CPD pin itself is a tri-state output and enters

tri-state whenever the converters are placed into the

Sleep Mode, Standby Mode, or when the charge

pump is disabled (when the Pump Disable bit, bit

D8 in the configuration register, is set). Once in tri-

state, the digital current can increase if this CPD

output floats near 1/2 digital supply. To ensure the

CPD pin stays near ground and to minimize the

digital current, add a 5MΩ resistor between it and

DGND (see Figure 1). If the resistor is left out, the

digital supply current may increase from 2 µA to 10

µA.

16

µ

F ensures very low ripple on NBV. Intrinsic

µ

F ceramic capac-

Voltage Reference

The CS5525/26 are specified for operation with a

2.5 V reference voltage between the VREF+ and

VREF- pins of the devices. For a single-ended ref-

erence voltage, such as the LT1019-2.5, the refer-

ence’s output is connected to the VREF+ pin of the

CS5525/26. The ground reference for the LT1019-

2.5 is connected to the VREF- pin.

The differential voltage between the VREF+ and

VREF- can be any voltage from 1.0 V up to 3.0 V,

however, the VREF- pin can not go below analog

ground.

Calibration

The CS5525/26 offer five different calibration

functions including self calibration and system cal-

ibration. However, after the CS5525/26 are reset,

they can perform measurements without being cal-

ibrated. In this case, the converters will utilize the

initialized values of the on-chip registers (Gain =

1.0, Offset = 0.0) to calculate output words for the

±100 mV range. Any initial offset and gain errors

in the internal circuitry of the chips will remain.

The gain and offset registers, which are used for

both self and system calibration, are used to set the

zero and full-scale points of the converter’s transfer

function. One LSB in the offset register is 2

portion of the input span (bipolar span is 2 times the

unipolar span). The MSB in the offset register de-

termines if the offset to be trimmed is positive or

negative (0 positive, 1 negative). The converters

can typically trim ±50 percent of the input span.

The gain register spans from 0 to (2 - 2

decimal equivalent meaning of the gain register is

where the binary numbers have a value of either

zero or one (b

Table

D

=

4

b

for details.

0

2

0

+

b

1

0

2

corresponds to the MSB). Refer to

1 –

+

b

2

2

2 –

+

CS5525 CS5526

…

+

b

N

2

–

N

=

i

∑

=

N

0

b

i

-23

DS202F5

2

i –

-24

). The

pro-