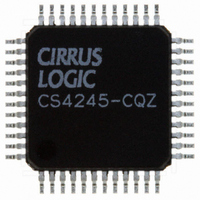

CS4245-CQZ Cirrus Logic Inc, CS4245-CQZ Datasheet - Page 35

CS4245-CQZ

Manufacturer Part Number

CS4245-CQZ

Description

IC CODEC AUD STER 104DB 48LQFP

Manufacturer

Cirrus Logic Inc

Type

Stereo Audior

Datasheet

1.CS4245-CQZ.pdf

(57 pages)

Specifications of CS4245-CQZ

Package / Case

48-LQFP

Data Interface

Serial

Resolution (bits)

24 b

Number Of Adcs / Dacs

2 / 2

Sigma Delta

Yes

Dynamic Range, Adcs / Dacs (db) Typ

104 / 104

Voltage - Supply, Analog

3.13 V ~ 5.25 V

Voltage - Supply, Digital

3.13 V ~ 5.25 V

Operating Temperature

-10°C ~ 70°C

Mounting Type

Surface Mount

Number Of Adc Inputs

12

Number Of Dac Outputs

4

Conversion Rate

192 KSPS

Interface Type

Serial (I2C, SPI)

Resolution

24 bit

Operating Supply Voltage

3.3 V, 5 V

Maximum Operating Temperature

+ 70 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 10 C

Number Of Channels

2 ADC/2 DAC

Thd Plus Noise

- 95 dB ADC / - 90 dB DAC

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

598-1501 - BOARD EVAL FOR CS4245 CODEC

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

598-1034

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CS4245-CQZ

Manufacturer:

CIRRUS

Quantity:

455

Part Number:

CS4245-CQZ

Manufacturer:

CIRRUS

Quantity:

20 000

Company:

Part Number:

CS4245-CQZR

Manufacturer:

Schneider

Quantity:

1 000

Company:

Part Number:

CS4245-CQZR

Manufacturer:

Cirrus Logic Inc

Quantity:

10 000

DS656F2

4.10

4.11

De-emphasis is only available in Single-Speed Mode.

Internal Digital Loopback

The CS4245 supports an internal digital loopback mode in which the output of the ADC is routed to the input

of the DAC. This mode may be activated by setting the LOOP bit in the Signal Selection register (See

tion 6.6 “Signal Selection - Address 06h” on page

ating at the same synchronous sample rate.

When this bit is set, the status of the DAC_DIF[1:0] bits in register 03h will be disregarded by the CS4245.

Any changes made to the DAC_DIF[1:0] bits while the LOOP bit is set will have no impact on operation until

the LOOP bit is cleared, at which time the Digital Interface Format of the DAC will operate according to the

format selected by the DAC_DIF[1:0] bits. While the LOOP bit is set, data will be present on the SDOUT pin

in the format selected by the ADC_DIF bit in register 04h.

Mute Control

The MUTEC pin becomes active during power-up initialization, reset, and muting if the MCLK2 to LRCK2

ratio is incorrect in Asynchronous Mode or the MCLK1 to LRCK2 ratio is incorrect in Synchronous Mode,

and during power-down. The MUTEC pin is intended to be used as control for an external mute circuit in

order to add off-chip mute capability.

Use of the Mute Control function is not mandatory, but recommended, for designs requiring the absolute

minimum in extraneous clicks and pops. Also, use of the Mute Control function can enable the system de-

-10dB

Gain

0dB

dB

Figure 15. De-Emphasis Curve

3.183 kHz

T1=50 µs

F1

45). To use this mode, the ADC and DAC must be oper-

10.61 kHz

F2

T2 = 15 µs

Frequency

CS4245

Sec-

35