ISPPAC-CLK5510V LATTICE [Lattice Semiconductor], ISPPAC-CLK5510V Datasheet - Page 38

ISPPAC-CLK5510V

Manufacturer Part Number

ISPPAC-CLK5510V

Description

In-System Programmable Clock Generator with Universal Fan-Out Buffer

Manufacturer

LATTICE [Lattice Semiconductor]

Datasheet

1.ISPPAC-CLK5510V.pdf

(43 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ISPPAC-CLK5510V-01T48C

Manufacturer:

Lattice Semiconductor Corporation

Quantity:

10 000

Company:

Part Number:

ISPPAC-CLK5510V-01T48I

Manufacturer:

Lattice Semiconductor Corporation

Quantity:

10 000

Company:

Part Number:

ISPPAC-CLK5510V-01TN48C

Manufacturer:

Lattice Semiconductor Corporation

Quantity:

10 000

Company:

Part Number:

ISPPAC-CLK5510V-01TN48I

Manufacturer:

SANYO

Quantity:

937

Company:

Part Number:

ISPPAC-CLK5510V-01TN48I

Manufacturer:

Lattice Semiconductor Corporation

Quantity:

10 000

Part Number:

ISPPAC-CLK5510V-01TN48I

Manufacturer:

LATTICE

Quantity:

20 000

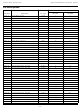

Lattice Semiconductor

ispClock5500 Family Data Sheet

VCCA, GNDA – These pins provide analog supply and ground for the ispClock5500 family’s internal analog cir-

cuitry, and should be bypassed with a 0.1uF capacitor as close to the pins as is practical. To improve noise immu-

nity, it is suggested that the supply to the VCCA pin be isolated from other circuitry with a ferrite bead.

VCCD, GNDD – These pins provide digital supply and ground for the ispClock5500 family’s internal digital circuitry,

and should be bypassed with a 0.1uF capacitor as close to the pins as is practical. to improve noise immunity it is

suggested that the supply to the VCCD pins be isolated with ferrite beads.

VCCJ – This pin provides power and a reference voltage for use by the JTAG interface circuitry. It may be set to

allow the ispClock5500 family devices to function in JTAG chains operating at voltages differing from VCCD.

REFA+, REFA-, REFB+, REFB- – These input pins provide the inputs for clock signals, and can accommodate

either single ended or differential signal protocols by using either just the ‘+’ pins, or both the ‘+’ and ‘-‘ pins. Two

sets of inputs are provided to accommodate the use of different signal sources and redundant clock sources.

REFSEL – This input pin is used to select which clock input pair (REFA+/- or REB+/-) is selected for use as the ref-

erence input. When REFSEL=0, REFA+/- is used, and when REFSEL=1, REFB+/- is used.

REFVTT – This pin is used to provide a termination voltage for the reference inputs when they are configured for

SSTL or HSTL logic, and should be connected to a suitable voltage supply in those cases.

TDO, TDI, TCK, TMS – These pins comprise the ispClock5500 device’s JTAG interface. The signal levels for these

pins are determined by the selection of the VCCJ voltage.

LOCK – This output pin indicates that the device’s PLL is in a locked condition when it goes low.

SGATE – This input pin provides a synchronous gating function for the outputs, which may be enabled on a bank-

by-bank basis. When the synchronous gating function is enabled for a given bank, that bank’s outputs will output a

clock signal when the SGATE pin is HIGH, and will drive a constant HIGH or LOW when the SGATE pin is LOW.

Synchronous gating ensures that when the state of SGATE is changed, no partial clock pulses will appear at the

outputs.

OEX, OEY – These pins are used to enable the outputs or put them into a high-impedance condition. Each output

may be set so that it is always on, always off, enabled by OEX or enabled by OEY.

GOE – Global output enable. This pin drives all outputs to a high-impedance state when it is pulled HIGH. GOE

also controls the internal feedback buffer, so that bringing GOE high will cause the PLL to lose lock.

PS0, PS1 – These input pins are used to select one of four user-defined configuration profiles for the device.

PLL_BYPASS – When this pin is pulled LOW, the V-dividers are driven from the output of the device’s VCO, and

the device behaves as a phase-locked loop. When this pin is pulled HIGH, the V-dividers are driven directly from

the output of the M-divider, and the PLL functions are effectively bypassed.

RESET – When this pin is pulled HIGH, all on-board counters are reset, and lock is lost.

TEST1,TEST2 – These pins are used for factory test functions, and should always be tied to ground.

n/c – These pins have no internal connection. We recommend that they be left unconnected.

RESERVED – These pins are reserved for factory use and should be left unconnected.

38