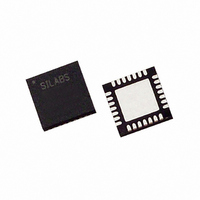

C8051F321-GM Silicon Laboratories Inc, C8051F321-GM Datasheet - Page 87

C8051F321-GM

Manufacturer Part Number

C8051F321-GM

Description

IC 8051 MCU 16K FLASH 28MLP

Manufacturer

Silicon Laboratories Inc

Series

C8051F32xr

Datasheets

1.C8051F320-TB.pdf

(250 pages)

2.C8051F321-GMR.pdf

(2 pages)

3.C8051F321-GM.pdf

(256 pages)

Specifications of C8051F321-GM

Program Memory Type

FLASH

Program Memory Size

16KB (16K x 8)

Package / Case

28-VQFN Exposed Pad, 28-HVQFN, 28-SQFN, 28-DHVQFN

Core Processor

8051

Core Size

8-Bit

Speed

25MHz

Connectivity

SMBus (2-Wire/I²C), SPI, UART/USART, USB

Peripherals

Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT

Number Of I /o

21

Ram Size

2.25K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 13x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Processor Series

C8051F3x

Core

8051

Data Bus Width

8 bit

Data Ram Size

2.25 KB

Interface Type

I2C/SMBus/SPI/UART/USB

Maximum Clock Frequency

25 MHz

Number Of Programmable I/os

21

Number Of Timers

4

Operating Supply Voltage

2.7 V to 3.6 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

PK51, CA51, A51, ULINK2

Development Tools By Supplier

C8051F320DK

Minimum Operating Temperature

- 40 C

On-chip Adc

13-ch x 10-bit or 17-ch x 10-bit

No. Of I/o's

21

Ram Memory Size

1280Byte

Cpu Speed

25MHz

No. Of Timers

4

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

336-1480 - DAUGHTER CARD TOOLSTCK C8051F321770-1006 - ISP 4PORT FOR SILABS C8051F MCU336-1449 - ADAPTER PROGRAM TOOLSTICK F321336-1260 - DEV KIT FOR C8051F320/F321

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

336-1261

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

C8051F321-GM

Manufacturer:

SiliconL

Quantity:

4 364

Part Number:

C8051F321-GM

Manufacturer:

SILICON LABS/èٹ¯ç§‘

Quantity:

20 000

Part Number:

C8051F321-GMR

Manufacturer:

SILICON LABS/èٹ¯ç§‘

Quantity:

20 000

9.3.

The CIP-51 includes an extended interrupt system supporting a total of 16 interrupt sources with two prior-

ity levels. The allocation of interrupt sources between on-chip peripherals and external inputs pins varies

according to the specific version of the device. Each interrupt source has one or more associated interrupt-

pending flag(s) located in an SFR. When a peripheral or external source meets a valid interrupt condition,

the associated interrupt-pending flag is set to logic 1.

If interrupts are enabled for the source, an interrupt request is generated when the interrupt-pending flag is

set. As soon as execution of the current instruction is complete, the CPU generates an LCALL to a prede-

termined address to begin execution of an interrupt service routine (ISR). Each ISR must end with an RETI

instruction, which returns program execution to the next instruction that would have been executed if the

interrupt request had not occurred. If interrupts are not enabled, the interrupt-pending flag is ignored by the

hardware and program execution continues as normal. (The interrupt-pending flag is set to logic 1 regard-

less of the interrupt's enable/disable state.)

Each interrupt source can be individually enabled or disabled through the use of an associated interrupt

enable bit in an SFR (IE-EIE2). However, interrupts must first be globally enabled by setting the EA bit

(IE.7) to logic 1 before the individual interrupt enables are recognized. Setting the EA bit to logic 0 disables

all interrupt sources regardless of the individual interrupt-enable settings.

Note: any instruction which clears the EA bit should be immediately followed by an instruction which has

two or more opcode bytes. For example:

// in 'C':

EA = 0;

EA = 0;

; in assembly:

CLR EA

CLR EA

If an interrupt is posted during the execution phase of a "CLR EA" opcode (or any instruction which clears

the EA bit), and the instruction is followed by a single-cycle instruction, the interrupt may be taken. If the

EA bit is read inside the interrupt service routine, it will return a '0'. When the "CLR EA" opcode is followed

by a multi-cycle instruction, the interrupt will not be taken.

Some interrupt-pending flags are automatically cleared by the hardware when the CPU vectors to the ISR.

However, most are not cleared by the hardware and must be cleared by software before returning from the

ISR. If an interrupt-pending flag remains set after the CPU completes the return-from-interrupt (RETI)

instruction, a new interrupt request will be generated immediately and the CPU will re-enter the ISR after

the completion of the next instruction.

9.3.1. MCU Interrupt Sources and Vectors

The MCU supports 16 interrupt sources. Software can simulate an interrupt by setting any interrupt-pend-

ing flag to logic 1. If interrupts are enabled for the flag, an interrupt request will be generated and the CPU

will vector to the ISR address associated with the interrupt-pending flag. MCU interrupt sources, associ-

ated vector addresses, priority order and control bits are summarized in Table 9.4 on page 89. Refer to the

datasheet section associated with a particular on-chip peripheral for information regarding valid interrupt

conditions for the peripheral and the behavior of its interrupt-pending flag(s).

Interrupt Handler

// clear EA bit

// ... followed by another 2-byte opcode

; clear EA bit

; ... followed by another 2-byte opcode

Rev. 1.4

C8051F320/1

87