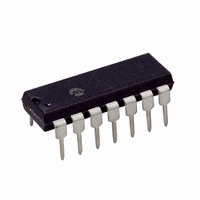

PIC16F688-I/P Microchip Technology, PIC16F688-I/P Datasheet - Page 121

PIC16F688-I/P

Manufacturer Part Number

PIC16F688-I/P

Description

IC PIC MCU FLASH 4KX14 14DIP

Manufacturer

Microchip Technology

Series

PIC® 16Fr

Datasheets

1.PIC16F616T-ISL.pdf

(8 pages)

2.PIC16F688T-ISL.pdf

(204 pages)

3.PIC16F688T-ISL.pdf

(6 pages)

4.PIC16F688T-ISL.pdf

(4 pages)

5.PIC16F688T-ISL.pdf

(688 pages)

6.PIC16F688-EP.pdf

(174 pages)

Specifications of PIC16F688-I/P

Program Memory Type

FLASH

Program Memory Size

7KB (4K x 14)

Package / Case

14-DIP (0.300", 7.62mm)

Core Processor

PIC

Core Size

8-Bit

Speed

20MHz

Connectivity

UART/USART

Peripherals

Brown-out Detect/Reset, POR, WDT

Number Of I /o

12

Eeprom Size

256 x 8

Ram Size

256 x 8

Voltage - Supply (vcc/vdd)

2 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Processor Series

PIC16F

Core

PIC

Data Bus Width

8 bit

Data Ram Size

256 B

Interface Type

SCI/USART

Maximum Clock Frequency

20 MHz

Number Of Programmable I/os

12

Number Of Timers

2

Operating Supply Voltage

2 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

Through Hole

3rd Party Development Tools

52715-96, 52716-328, 52717-734

Development Tools By Supplier

PG164130, DV164035, DV244005, DV164005, PG164120, ICE2000, DM163014, DM164120-4

Minimum Operating Temperature

- 40 C

On-chip Adc

8-ch x 10-bit

Data Rom Size

256 B

Height

3.3 mm

Length

19.05 mm

Supply Voltage (max)

5.5 V

Supply Voltage (min)

2 V

Width

6.35 mm

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

AC162066 - HEADER INTRFC MPLAB ICD2 20PINAC162061 - HEADER INTRFC MPLAB ICD2 20PINDM163029 - BOARD PICDEM FOR MECHATRONICSAC162056 - HEADER INTERFACE ICD2 16F688ACICE0207 - MPLABICE 14P 300 MIL ADAPTERAC124001 - MODULE SKT PROMATEII 8DIP/SOIC

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

PIC16F688-I/P

Manufacturer:

MICROCHIP

Quantity:

26

Company:

Part Number:

PIC16F688-I/P

Manufacturer:

MOT

Quantity:

61

11.3

The PIC16F688 has multiple sources of interrupt:

• External Interrupt RA2/INT

• TMR0 Overflow Interrupt

• PORTA Change Interrupts

• 2 Comparator Interrupts

• A/D Interrupt

• Timer1 Overflow Interrupt

• EEPROM Data Write Interrupt

• Fail-Safe Clock Monitor Interrupt

• EUSART Receive and Transmit interrupts

The Interrupt Control (INTCON) register and Peripheral

Interrupt Request 1 (PIR1) register record individual

interrupt requests in flag bits. The INTCON register

also has individual and global interrupt enable bits.

A Global Interrupt Enable bit, GIE bit of the INTCON

register, enables (if set) all unmasked interrupts, or dis-

ables (if cleared) all interrupts. Individual interrupts can

be disabled through their corresponding enable bits in

the INTCON register and PIE1 register. GIE is cleared

on Reset.

The Return from Interrupt instruction, RETFIE, exits

the interrupt routine, as well as sets the GIE bit, which

re-enables unmasked interrupts.

The following interrupt flags are contained in the

INTCON register:

• INT Pin Interrupt

• PORTA Change Interrupt

• TMR0 Overflow Interrupt

The peripheral interrupt flags are contained in the

special register, PIR1. The corresponding interrupt

enable bit is contained in special register, PIE1.

The following interrupt flags are contained in the PIR1

register:

• EEPROM Data Write Interrupt

• A/D Interrupt

• EUSART Receive and Transmit Interrupts

• 2 Comparator Interrupts

• Timer1 Overflow Interrupt

• Fail-Safe Clock Monitor Interrupt

When an interrupt is serviced:

• The GIE is cleared to disable any further interrupt.

• The return address is pushed onto the stack.

• The PC is loaded with 0004h.

© 2009 Microchip Technology Inc.

Interrupts

For external interrupt events, such as the INT pin or

PORTA change interrupt, the interrupt latency will be

three or four instruction cycles. The exact latency

depends upon when the interrupt event occurs (see

Figure 11-8). The latency is the same for one or

two-cycle instructions. Once in the Interrupt Service

Routine, the source(s) of the interrupt can be

determined by polling the interrupt flag bits. The

interrupt flag bit(s) must be cleared in software before

re-enabling interrupts to avoid multiple interrupt

requests.

For additional information on Timer1, A/D or data

EEPROM modules, refer to the respective peripheral

section.

Note 1: Individual interrupt flag bits are set,

2: When an instruction that clears the GIE

regardless

corresponding mask bit or the GIE bit.

bit is executed, any interrupts that were

pending for execution in the next cycle

are ignored. The interrupts, which were

ignored, are still pending to be serviced

when the GIE bit is set again.

of

PIC16F688

the

DS41203E-page 119

status

of

their