AT91SAM7X512-CU Atmel, AT91SAM7X512-CU Datasheet - Page 568

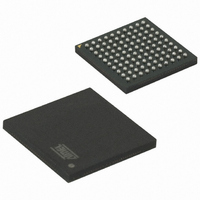

AT91SAM7X512-CU

Manufacturer Part Number

AT91SAM7X512-CU

Description

MCU ARM 512K HS FLASH 100-TFBGA

Manufacturer

Atmel

Series

AT91SAMr

Datasheet

1.AT91SAM7X512-AU-999.pdf

(687 pages)

Specifications of AT91SAM7X512-CU

Core Processor

ARM7

Core Size

16/32-Bit

Speed

55MHz

Connectivity

CAN, Ethernet, I²C, SPI, SSC, UART/USART, USB

Peripherals

Brown-out Detect/Reset, DMA, POR, PWM, WDT

Number Of I /o

62

Program Memory Size

512KB (512K x 8)

Program Memory Type

FLASH

Ram Size

128K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 1.95 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Processor Series

AT91SAMx

Core

ARM7TDMI

Data Bus Width

32 bit

Data Ram Size

128 KB

Interface Type

CAN, SPI, SSC, TWI, USART, USB

Maximum Clock Frequency

55 MHz

Number Of Programmable I/os

13

Number Of Timers

3

Operating Supply Voltage

3 V to 3.6 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

JTRACE-ARM-2M, KSK-AT91SAM7X-PL, MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

AT91SAM-ICE, AT91-ISP, AT91SAM7X-EK

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit

Package

100TFBGA

Device Core

ARM7TDMI

Family Name

91S

Maximum Speed

55 MHz

Cpu Family

91S

Device Core Size

32b

Frequency (max)

55MHz

Total Internal Ram Size

128KB

# I/os (max)

62

Number Of Timers - General Purpose

3

Operating Supply Voltage (typ)

1.8/3.3V

Operating Supply Voltage (max)

1.95/3.6V

Operating Supply Voltage (min)

1.65/3V

Instruction Set Architecture

RISC

Operating Temp Range

-40C to 85C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

100

Package Type

TFBGA

For Use With

AT91SAM-ICE - EMULATOR FOR AT91 ARM7/ARM9AT91SAM7X-EK - KIT EVAL FOR AT91SAM7X256/128

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 568 of 687

- Download datasheet (11Mb)

Table 37-2.

568

31:0

Bit

31

30

AT91SAM7X512/256/128 Preliminary

Byte Address of buffer

Used. Needs to be zero for the EMAC to read data from the transmit buffer. The EMAC sets this to one for the first buffer

of a frame once it has been successfully transmitted.

Software has to clear this bit before the buffer can be used again.

Note:

Wrap. Marks last descriptor in transmit buffer descriptor list.

Transmit Buffer Descriptor Entry

This bit is only set for the first buffer in a frame unlike receive where all buffers have the Used bit set once used.

the control word is read if transmission is to happen. It is written to one when a frame has been

transmitted. Bits 27, 28 and 29 indicate various transmit error conditions. Bit 30 is the “wrap” bit

which can be set for any buffer within a frame. If no wrap bit is encountered after 1024 descrip-

tors, the queue pointer rolls over to the start in a similar fashion to the receive queue.

The transmit buffer queue pointer register must not be written while transmit is active. If a new

value is written to the transmit buffer queue pointer register, the queue pointer resets itself to

point to the beginning of the new queue. If transmit is disabled by writing to bit 3 of the network

control, the transmit buffer queue pointer register resets to point to the beginning of the transmit

queue. Note that disabling receive does not have the same effect on the receive queue pointer.

Once the transmit queue is initialized, transmit is activated by writing to bit 9, the Transmit Start

bit of the network control register. Transmit is halted when a buffer descriptor with its used bit set

is read, or if a transmit error occurs, or by writing to the transmit halt bit of the network control

register. (Transmission is suspended if a pause frame is received while the pause enable bit is

set in the network configuration register.) Rewriting the start bit while transmission is active is

allowed.

Transmission control is implemented with a Tx_go variable which is readable in the transmit sta-

tus register at bit location 3. The Tx_go variable is reset when:

To set tx_go, write to bit 9, tx_start, of the network control register. Transmit halt does not take

effect until any ongoing transmit finishes. If a collision occurs during transmission of a multi-

buffer frame, transmission automatically restarts from the first buffer of the frame. If a “used” bit

is read midway through transmission of a multi-buffer frame, this is treated as a transmit error.

Transmission stops, tx_er is asserted and the FCS is bad.

If transmission stops due to a transmit error, the transmit queue pointer resets to point to the

beginning of the transmit queue. Software needs to re-initialize the transmit queue after a trans-

mit error.

If transmission stops due to a “used” bit being read at the start of the frame, the transmission

queue pointer is not reset and transmit starts from the same transmit buffer descriptor when the

transmit start bit is written

– transmit is disabled

– a buffer descriptor with its ownership bit set is read

– a new value is written to the transmit buffer queue pointer register

– bit 10, tx_halt, of the network control register is written

– there is a transmit error such as too many retries or a transmit underrun.

Word 0

Word 1

Function

6120H–ATARM–17-Feb-09

Related parts for AT91SAM7X512-CU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT EVAL FOR AT91SAM7X256/128

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools KICKSTART KIT ATMEL AT91SAM7X

Manufacturer:

IAR Systems

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Flash Microcontroller

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

2-Wire Serial EEPROM

Manufacturer:

ATMEL Corporation

Datasheet: