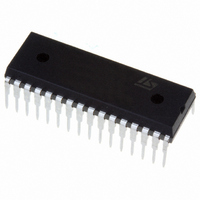

ST72F262G2B5 STMicroelectronics, ST72F262G2B5 Datasheet - Page 48

ST72F262G2B5

Manufacturer Part Number

ST72F262G2B5

Description

IC MCU 8BIT 8K FLASH 32-SDIP

Manufacturer

STMicroelectronics

Series

ST7r

Datasheet

1.STEVAL-ISQ002V1.pdf

(172 pages)

Specifications of ST72F262G2B5

Core Processor

ST7

Core Size

8-Bit

Speed

16MHz

Connectivity

SPI

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

22

Program Memory Size

8KB (8K x 8)

Program Memory Type

FLASH

Ram Size

256 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 6x10b

Oscillator Type

Internal

Operating Temperature

-10°C ~ 85°C

Package / Case

32-SDIP (0.400", 10.16mm)

Processor Series

ST72F2x

Core

ST7

Data Bus Width

8 bit

Data Ram Size

256 B

Interface Type

I2C, SCI, SPI

Maximum Clock Frequency

8 MHz

Number Of Programmable I/os

22

Number Of Timers

16 bit

Maximum Operating Temperature

+ 85 C

Mounting Style

Through Hole

Development Tools By Supplier

ST7F264-IND/USB, ST72F34X-SK/RAIS, ST7MDT10-DVP3, ST7MDT10-EMU3, STX-RLINK

Minimum Operating Temperature

- 40 C

On-chip Adc

8 bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ST72F262G2B5

Manufacturer:

TAIYO

Quantity:

8 122

ST72260Gx, ST72262Gx, ST72264Gx

11 ON-CHIP PERIPHERALS

11.1 WATCHDOG TIMER (WDG)

11.1.1 Introduction

The Watchdog timer is used to detect the occur-

rence of a software fault, usually generated by ex-

ternal interference or by unforeseen logical condi-

tions, which causes the application program to

abandon its normal sequence. The Watchdog cir-

cuit generates an MCU reset on expiry of a pro-

grammed time period, unless the program refresh-

es the counter’s contents before the T6 bit be-

comes cleared.

11.1.2 Main Features

■

■

■

■

■

11.1.3 Functional Description

The counter value stored in the Watchdog Control

register (WDGCR bits T[6:0]), is decremented

every 16384 f

length of the timeout period can be programmed

by the user in 64 increments.

Figure 31. Watchdog Block Diagram

48/172

MCC/RTC

Programmable free-running downcounter

Programmable reset

Reset (if watchdog activated) when the T6 bit

reaches zero

Optional

(configurable by option byte)

Hardware Watchdog selectable by option byte

11

MSB

RTC COUNTER

12-BIT MCC

reset

f

DIV 64

OSC2

OSC2

6

5

LSB

cycles (approx.), and the

on

0

HALT

TB[1:0] bits

(MCCSR

Register)

instruction

WDGA

RESET

T6

If the watchdog is activated (the WDGA bit is set)

and when the 7-bit timer (bits T[6:0]) rolls over

from 40h to 3Fh (T6 becomes cleared), it initiates

a reset cycle pulling low the reset pin for typically

500ns.

The application program must write in the

WDGCR register at regular intervals during normal

operation to prevent an MCU reset. This down-

counter is free-running: it counts down even if the

watchdog is disabled. The value to be stored in the

WDGCR register must be between FFh and C0h:

– The WDGA bit is set (watchdog enabled)

– The T6 bit is set to prevent generating an imme-

– The T[5:0] bits contain the number of increments

Following a reset, the watchdog is disabled. Once

activated it cannot be disabled, except by a reset.

The T6 bit can be used to generate a software re-

set (the WDGA bit is set and the T6 bit is cleared).

If the watchdog is activated, the HALT instruction

will generate a Reset.

WATCHDOG CONTROL REGISTER (WDGCR)

diate reset

which represents the time delay before the

watchdog produces a reset (see

proximate Timeout

between a minimum and a maximum value due

to the unknown status of the prescaler when writ-

ing to the WDGCR register (see

T5

6-BIT DOWNCOUNTER (CNT)

WDG PRESCALER

T4

DIV 4

T3

Duration). The timing varies

T2

T1

Figure

Figure 32. Ap-

T0

33).