C8051F313-GMR Silicon Laboratories Inc, C8051F313-GMR Datasheet - Page 187

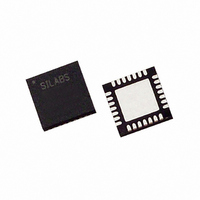

C8051F313-GMR

Manufacturer Part Number

C8051F313-GMR

Description

IC 8051 MCU 8K FLASH 28MLP

Manufacturer

Silicon Laboratories Inc

Series

C8051F31xr

Specifications of C8051F313-GMR

Core Processor

8051

Core Size

8-Bit

Speed

25MHz

Connectivity

SMBus (2-Wire/I²C), SPI, UART/USART

Peripherals

POR, PWM, Temp Sensor, WDT

Number Of I /o

25

Program Memory Size

8KB (8K x 8)

Program Memory Type

FLASH

Ram Size

1.25K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 17x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

28-VQFN Exposed Pad, 28-HVQFN, 28-SQFN, 28-DHVQFN

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

- Current page: 187 of 228

- Download datasheet (2Mb)

17. Timers

Each MCU includes four counter/timers: two are 16-bit counter/timers compatible with those found in the

standard 8051, and two are 16-bit auto-reload timer for use with the ADC, SMBus, or for general purpose

use. These timers can be used to measure time intervals, count external events and generate periodic

interrupt requests. Timer 0 and Timer 1 are nearly identical and have four primary modes of operation.

Timer 2 and Timer 3 offer 16-bit and split 8-bit timer functionality with auto-reload.

Timers 0 and 1 may be clocked by one of five sources, determined by the Timer Mode Select bits (T1M-

T0M) and the Clock Scale bits (SCA1-SCA0). The Clock Scale bits define a pre-scaled clock from which

Timer 0 and/or Timer 1 may be clocked (See SFR Definition 17.3 for pre-scaled clock selection).

Timer 0/1 may then be configured to use this pre-scaled clock signal or the system clock. Timer 2 and

Timer 3 may be clocked by the system clock, the system clock divided by 12, or the external oscillator

clock source divided by 8.

Timer 0 and Timer 1 may also be operated as counters. When functioning as a counter, a counter/timer

register is incremented on each high-to-low transition at the selected input pin (T0 or T1). Events with a fre-

quency of up to one-fourth the system clock's frequency can be counted. The input signal need not be peri-

odic, but it should be held at a given level for at least two full system clock cycles to ensure the level is

properly sampled.

17.1. Timer 0 and Timer 1

Each timer is implemented as 16-bit register accessed as two separate bytes: a low byte (TL0 or TL1) and

a high byte (TH0 or TH1). The Counter/Timer Control register (TCON) is used to enable Timer 0 and Timer

1 as well as indicate status. Timer 0 interrupts can be enabled by setting the ET0 bit in the IE register (SFR

Definition 8.7. “IE: Interrupt Enable” on page 97); Timer 1 interrupts can be enabled by setting the ET1 bit

in the IE register. Both counter/timers operate in one of four primary modes selected by setting the Mode

Select bits T1M1-T0M0 in the Counter/Timer Mode register (TMOD). Each timer can be configured inde-

pendently. Each operating mode is described below.

17.1.1. Mode 0: 13-bit Counter/Timer

Timer 0 and Timer 1 operate as 13-bit counter/timers in Mode 0. The following describes the configuration

and operation of Timer 0. However, both timers operate identically, and Timer 1 is configured in the same

manner as described for Timer 0.

The TH0 register holds the eight MSBs of the 13-bit counter/timer. TL0 holds the five LSBs in bit positions

TL0.4–TL0.0. The three upper bits of TL0 (TL0.7–TL0.5) are indeterminate and should be masked out or

ignored when reading. As the 13-bit timer register increments and overflows from 0x1FFF (all ones) to

0x0000, the timer overflow flag TF0 (TCON.5) is set and an interrupt will occur if Timer 0 interrupts are

enabled.

Timer 0 and Timer 1 Modes:

Two 8-bit counter/timers

13-bit counter/timer

16-bit counter/timer

8-bit counter/timer

with auto-reload

(Timer 0 only)

Two 8-bit timers with auto-reload

16-bit timer with auto-reload

Timer 2 Modes:

Rev. 1.7

C8051F310/1/2/3/4/5/6/7

Two 8-bit timers with auto-reload

16-bit timer with auto-reload

Timer 3 Modes:

187

Related parts for C8051F313-GMR

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

SMD/C°/SINGLE-ENDED OUTPUT SILICON OSCILLATOR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 AES KEYFOB DEMO WITH LCD RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 SIMPLIFIED KEY FOB DEMO WITH LED RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A/-40 TO 85 OC/EZLINK MODULE; F930/4432 HIGH BAND (REV E/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

EZLink Module; F930/4432 Low Band (rev e/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4460 10 DBM RADIO TEST CARD 434 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4461 14 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RFSWITCH RADIO TEST CARD 460 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 27 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 SKYWORKS 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

N/A N/A/-40 TO 85 OC/4463 RFMD 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 169 MHZ

Manufacturer:

Silicon Laboratories Inc