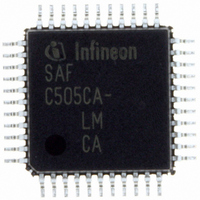

SAF-C515C-8EM CA Infineon Technologies, SAF-C515C-8EM CA Datasheet - Page 21

SAF-C515C-8EM CA

Manufacturer Part Number

SAF-C515C-8EM CA

Description

IC MCU 8BIT OTP MQFP-80-1

Manufacturer

Infineon Technologies

Series

C5xx/C8xxr

Datasheet

1.SAF-C515C-8EM_CA.pdf

(96 pages)

Specifications of SAF-C515C-8EM CA

Core Processor

C500

Core Size

8-Bit

Speed

10MHz

Connectivity

CAN, EBI/EMI, SPI, UART/USART

Peripherals

POR, PWM, WDT

Number Of I /o

49

Program Memory Size

64KB (64K x 8)

Program Memory Type

OTP

Ram Size

2.5K x 8

Voltage - Supply (vcc/vdd)

4.25 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Package / Case

80-SQFP

Data Bus Width

8 bit

Data Ram Size

2.25 KB

Interface Type

USART, SSC

Maximum Clock Frequency

10 MHz

Number Of Programmable I/os

49

Number Of Timers

3

Operating Supply Voltage

5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 8 Channel

Packages

PG-MQFP-80

Max Clock Frequency

10.0 MHz

Sram (incl. Cache)

2.25 KByte

Can Nodes

1

A / D Input Lines (incl. Fadc)

8

Program Memory

64.0 KByte

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

F515C8EMCANP

F515C8EMCAXT

SAF-C515C-8EMCA

SAF-C515C-8EMCA

SAF-C515C-8EMCAIN

SAFC515C8EMCAX

SP000068749

SP000106399

F515C8EMCAXT

SAF-C515C-8EMCA

SAF-C515C-8EMCA

SAF-C515C-8EMCAIN

SAFC515C8EMCAX

SP000068749

SP000106399

Control of XRAM/CAN Controller Access

The XRAM in the C515C is a memory area that is logically located at the upper end of

the external memory space, but is integrated on the chip. Because the XRAM and the

CAN controller is used in the same way as external data memory the same instruction

types (MOVX) must be used for accessing the XRAM. Two bits in SFR SYSCON,

XMAP0 and XMAP1, control the accesses to the XRAM and the CAN controller.

SYSCON

Special Function Register

Bit

XMAP1

XMAP0

Bit XMAP0 is hardware protected. If it is reset once (XRAM/CAN controller access

enabled) it cannot be set by software. Only a reset operation will set the XMAP0 bit

again.

Data Sheet

Bit No. MSB

B1 H

The function of the shaded bits is not described in this section.

7

–

Function

XRAM/CAN controller visible access control

Control bit for RD/WR signals during XRAM/CAN Controller

accesses. If addresses are outside the XRAM/CAN controller

address range or if XRAM is disabled, this bit has no effect.

XMAP1 = 0: The signals RD and WR are not activated during

XMAP1 = 1: Ports 0, 2 and the signals RD and WR are activated

Global XRAM/CAN controller access enable/disable control

XMAP0 = 0: The access to XRAM and CAN controller is enabled.

XMAP0 = 1: The access to XRAM and CAN controller is disabled

PMOD

6

EALE RMAP

5

accesses to the XRAM/CAN Controller

during accesses to XRAM/CAN Controller. In this

mode, address and data information during

XRAM/CAN Controller accesses are visible externally.

(default after reset). All MOVX accesses are

performed via the external bus. Further, this bit is

hardware protected.

4

(B1

17

H

3

–

)

C515C-8R Reset Value: X010XX01

C515C-8E Reset Value: X010X001

CSWO XMAP1

2

1

XMAP0

LSB

0

SYSCON

C515C

2003-02

B

B