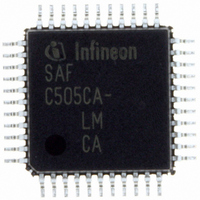

SAF-C515C-8EM CA Infineon Technologies, SAF-C515C-8EM CA Datasheet - Page 86

SAF-C515C-8EM CA

Manufacturer Part Number

SAF-C515C-8EM CA

Description

IC MCU 8BIT OTP MQFP-80-1

Manufacturer

Infineon Technologies

Series

C5xx/C8xxr

Datasheet

1.SAF-C515C-8EM_CA.pdf

(96 pages)

Specifications of SAF-C515C-8EM CA

Core Processor

C500

Core Size

8-Bit

Speed

10MHz

Connectivity

CAN, EBI/EMI, SPI, UART/USART

Peripherals

POR, PWM, WDT

Number Of I /o

49

Program Memory Size

64KB (64K x 8)

Program Memory Type

OTP

Ram Size

2.5K x 8

Voltage - Supply (vcc/vdd)

4.25 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Package / Case

80-SQFP

Data Bus Width

8 bit

Data Ram Size

2.25 KB

Interface Type

USART, SSC

Maximum Clock Frequency

10 MHz

Number Of Programmable I/os

49

Number Of Timers

3

Operating Supply Voltage

5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 8 Channel

Packages

PG-MQFP-80

Max Clock Frequency

10.0 MHz

Sram (incl. Cache)

2.25 KByte

Can Nodes

1

A / D Input Lines (incl. Fadc)

8

Program Memory

64.0 KByte

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

F515C8EMCANP

F515C8EMCAXT

SAF-C515C-8EMCA

SAF-C515C-8EMCA

SAF-C515C-8EMCAIN

SAFC515C8EMCAX

SP000068749

SP000106399

F515C8EMCAXT

SAF-C515C-8EMCA

SAF-C515C-8EMCA

SAF-C515C-8EMCAIN

SAFC515C8EMCAX

SP000068749

SP000106399

Figure 34

Notes:

1. Shown is the data/clock relationship for CPOL = CPHA = 1. The timing diagram is

2. In the case of slave mode and CPHA = 0, the output delay for the MSB applies to the

3. In the case of master mode and CPHA = 0, the MSB becomes valid after the data

Data Sheet

valid for the other cases accordingly.

falling edge of SLS (if transmitter is enabled).

has been written into the shift register, i.e. at least one half SCLK clock cycle before

the first clock transition.

SCLK

STO

SRI

TC

SSC Timing

t

D

t

SCL

t

S

MSB

t

SCLK

t

HI

MSB

t

SCH

t

HD

82

LSB

LSB

t

DTC

MCT02417

C515C

2003-02