PIC12C672/JW Microchip Technology, PIC12C672/JW Datasheet - Page 317

PIC12C672/JW

Manufacturer Part Number

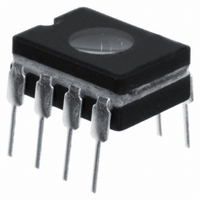

PIC12C672/JW

Description

IC MCU EPROM 2KX14 A/D 8CDIP

Manufacturer

Microchip Technology

Series

PIC® 12Cr

Datasheets

1.PIC16F688T-ISL.pdf

(688 pages)

2.PIC12CE673-10P.pdf

(129 pages)

3.PIC12CE673-10P.pdf

(14 pages)

Specifications of PIC12C672/JW

Core Processor

PIC

Core Size

8-Bit

Speed

10MHz

Peripherals

POR, WDT

Number Of I /o

5

Program Memory Size

3.5KB (2K x 14)

Program Memory Type

EPROM, UV

Ram Size

128 x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 4x8b

Oscillator Type

Internal

Operating Temperature

0°C ~ 70°C

Package / Case

8-CDIP (0.300", 7.62mm) Window

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Eeprom Size

-

Connectivity

-

Other names

Q395827

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

PIC12C672/JW

Manufacturer:

MICKO

Quantity:

2 100

- Current page: 317 of 688

- Download datasheet (3Mb)

17.4.12

17.4.12.1 BF Status Flag

17.4.12.2 SSPOV Status Flag

17.4.12.3 WCOL Status Flag

1997 Microchip Technology Inc.

I

2

C Master Mode Reception

Master mode reception is enabled by programming the receive enable bit, RCEN

(SSPCON2<3>).

The baud rate generator begins counting, and on each rollover, the state of the SCL pin changes

(high to low/low to high), and data is shifted into the SSPSR. After the falling edge of the eighth

clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into

the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set, and the baud rate generator is sus-

pended from counting, holding SCL low. The SSP is now in IDLE state, awaiting the next com-

mand. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can

then send an acknowledge bit at the end of reception, by setting the acknowledge sequence

enable bit, ACKEN (SSPCON2<4>).

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from

SSPSR. It is cleared when the SSPBUF register is read.

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR, and the BF

flag bit is already set from a previous reception.

If the user writes the SSPBUF when a receive is already in progress (i.e. SSPSR is still shifting

in a data byte), then the WCOL bit is set and the contents of the buffer are unchanged (the write

doesn’t occur).

Note:

The SSP Module must be in an IDLE STATE before the RCEN bit is set, or the

RCEN bit will be disregarded.

Preliminary

Section 17. MSSP

DS31017A-page 17-41

17

Related parts for PIC12C672/JW

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

8-Pin/ 8-Bit CMOS Microcontroller with EEPROM Data Memory

Manufacturer:

Microchip Technology

Part Number:

Description:

IC, 8BIT MCU, PIC12, 32MHZ, DFN-8

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

IC, 8BIT MCU, PIC12, 32MHZ, DFN-8

Manufacturer:

Microchip Technology

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet:

Part Number:

Description:

Manufacturer:

Microchip Technology Inc.

Datasheet: