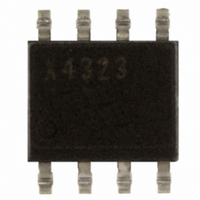

X4323S8I Intersil, X4323S8I Datasheet - Page 15

X4323S8I

Manufacturer Part Number

X4323S8I

Description

IC CPU SUPRV 32K EE RST LO 8SOIC

Manufacturer

Intersil

Type

Simple Reset/Power-On Resetr

Datasheet

1.X4323S8.pdf

(22 pages)

Specifications of X4323S8I

Number Of Voltages Monitored

1

Output

Open Drain or Open Collector

Reset

Active Low

Reset Timeout

100 ms Minimum

Voltage - Threshold

4.38V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

8-SOIC

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

X4323S8I

Manufacturer:

Intersil

Quantity:

1 550

Company:

Part Number:

X4323S8I-2.7

Manufacturer:

Intersil

Quantity:

284

Figure 15. X4323, X4325 Addressing

Operational Notes

The device powers-up in the following state:

– The device is in the low power standby state.

– The WEL bit is set to ‘0’. In this state it is not possi-

– SDA pin is the input mode.

– RESET Signal is active for t

Data Protection

The following circuitry has been included to prevent

inadvertent writes:

– The WEL bit must be set to allow write operations.

– The proper clock count and bit sequence is required

– A three step sequence is required before writing into

– The WP pin, when held HIGH, and WPEN bit at logic

ble to write to the device.

prior to the stop bit in order to start a nonvolatile

write cycle.

the Control Register to change Watchdog Timer or

Block Lock settings.

HIGH will prevent all writes to the Control Register.

15

(X1)

D7

A7

1

0

PURST

Device Identifier

(X0)

D6

A6

0

0

.

Word Address Byte 0 for all options

(Y5)

D5

A5

Word Address Byte 0–32K

1

0

Low Order Word Address

Data Byte for all options

Slave Address Byte

(Y4)

D4

A4

0

0

X4323, X4325

(X5)

A11

(Y3)

D3

A3

0

High Order Word Address

Device Select

A10

(X4)

(Y2)

S1

D2

A2

– Communication to the device is inhibited while

– Block Lock bits can protect sections of the memory

SYMBOL TABLE

RESET/RESET is active and any in-progress com-

munication is terminated.

array from write operations.

WAVEFORM

(Y1)

(X3)

S0

A9

A1

D1

R/W

(X2)

(Y0)

A8

A0

D0

INPUTS

Must be

steady

May change

from LOW

to HIGH

May change

from HIGH

to LOW

Don’t Care:

Changes

Allowed

N/A

OUTPUTS

Will be

steady

Will change

from LOW

to HIGH

Will change

from HIGH

to LOW

Changing:

State Not

Known

Center Line

is High

Impedance

May 25, 2006

FN8122.1