SI4030-A0-FM Silicon Laboratories Inc, SI4030-A0-FM Datasheet

SI4030-A0-FM

Specifications of SI4030-A0-FM

Available stocks

Related parts for SI4030-A0-FM

SI4030-A0-FM Summary of contents

Page 1

Si4330 ISM R ECEIVER Features Frequency Range = 240–960 MHz Sensitivity = –121 dBm Low Power Consumption 18.5 mA receive Data Rate = 0.123 to 256 kbps FSK, GFSK, and OOK modulation Power ...

Page 2

Si4330-B1 Functional Block Diagram 2 Rev 1.0 ...

Page 3

T C ABLE O F ONTENTS Section 1. Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 4

Si4330-B1 8.6. Wake-Up Timer and 32 kHz Clock Source . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 5

IGURES Figure 1. RX Application Example............................................................................................ 14 Figure 2. SPI Timing.................................................................................................................. 16 Figure 3. SPI Timing—READ Mode ..........................................................................................17 Figure 4. SPI Timing—Burst Write Mode .................................................................................. 17 Figure 5. SPI Timing—Burst Read Mode .................................................................................. 17 ...

Page 6

ABLES 1 Table 1. DC Characteristics ......................................................................................................7 Table 2. Synthesizer AC Electrical Characteristics Table 3. Receiver AC Electrical Characteristics Table 4. Auxiliary Block Specifications Table 5. Digital IO Specifications (SDO, SDI, SCLK, nSEL, and ...

Page 7

Electrical Specifications 1 Table 1. DC Characteristics Parameter Symbol Supply Voltage Range V DD Power Saving Modes I Shutdown I Standby I Sleep I Sensor-LBD I Sensor-TS I Ready TUNE Mode Current I Tune RX Mode Current I RX ...

Page 8

Si4330-B1 Table 2. Synthesizer AC Electrical Characteristics Parameter Symbol Synthesizer Frequency F SYN Range Synthesizer Frequency F RES-LB 2 Resolution F RES-HB Reference Frequency f REF_LV 2 Input Level 2 Synthesizer Settling Time t LOCK 2 F Residual FM RMS ...

Page 9

Table 3. Receiver AC Electrical Characteristics Parameter Symbol RX Frequency F RX Range 2 RX Sensitivity P RX_2 P RX_40 P RX_100 P RX_125 P RX_OOK 3 RX Channel Bandwidth BW BER Variation vs Power P RX_RES 3 Level 3 ...

Page 10

Si4330-B1 Table 4. Auxiliary Block Specifications Parameter Symbol Temperature Sensor TS 2 Accuracy Temperature Sensor TS 2 Sensitivity Low Battery Detector LBD 2 Resolution Low Battery Detector LBD 2 Conversion Time Microcontroller Clock F MC Output Frequency General Purpose ADC ...

Page 11

Table 5. Digital IO Specifications (SDO, SDI, SCLK, nSEL, and nIRQ) Parameter Symbol Rise Time T Fall Time T Input Capacitance Logic High Level Input Voltage Logic Low Level Input Voltage Input Current Logic High Level Output Voltage Logic Low ...

Page 12

Si4330-B1 Table 7. Absolute Maximum Ratings V to GND DD Voltage on Digital Control Inputs Voltage on Analog Inputs RX Input Power Operating Ambient Temperature Range T Thermal Impedance JA Junction Temperature T J Storage Temperature Range T STG ...

Page 13

Definition of Test Conditions Production Test Conditions: +25 °C A +3.3 VDC DD Sensitivity measured at 919 MHz External reference signal (XOUT) = 1.0 V Production test schematic (unless noted ...

Page 14

Si4330-B1 2. Functional Description The Si4330 is an ISM wireless receiver with continuous frequency tuning over the specified bands which encompasses from 240–960 MHz. The wide operating voltage range of 1.8–3.6 V and low current consumption makes the Si4330 an ...

Page 15

Operating Modes The Si4330 provides several operating modes which can be used to optimize the power consumption for a given application. Depending upon the system communication protocol, an optimal trade-off between the radio wake time and power consumption can ...

Page 16

Si4330-B1 3. Controller Interface 3.1. Serial Peripheral Interface (SPI) The Si4330 communicates with the host MCU over a standard 3-wire SPI interface: SCLK, SDI, and nSEL. The host MCU can read data from the device on the SDO output pin. ...

Page 17

First Bit RW SDI SCLK SDO nSEL The SPI interface contains a burst read/write mode which allows for reading/writing sequential registers without having to re-send the SPI address. When the nSEL bit is held low while continuing ...

Page 18

Si4330-B1 3.2. Operating Mode Control There are three primary states in the Si4330 radio state machine: SHUTDOWN, IDLE, and RX (see Figure 6). The SHUTDOWN state completely shuts down the radio to minimize current consumption. There are five different configurations/options ...

Page 19

SHUTDOWN State The SHUTDOWN state is the lowest current consumption state of the device with nominally less than current consumption. The SHUTDOWN state may be entered by driving the SDN pin (Pin 20) high. The SDN ...

Page 20

Si4330-B1 3.2.3. RX State The RX state may be entered from any of the IDLE modes when the rxon bit is set "Register 07h. Operating Mode and Function Control 1". A built-in sequencer takes care of all ...

Page 21

Interrupts The Si4330 is capable of generating an interrupt signal when certain events occur. The chip notifies the microcontroller that an interrupt event has occurred by setting the nIRQ output pin LOW = 0. This interrupt signal will be ...

Page 22

Si4330-B1 3.4. System Timing The system timing for RX mode is shown in Figure 7. The user only needs to program the desired mode, and the internal sequencer will properly transition the part from its current mode. The VCO will ...

Page 23

Frequency Control For calculating the necessary frequency register settings it is recommended that customers use Silicon Labs’ Wireless Design Suite (WDS) or the EZRadioPRO Register Calculator worksheet (in Microsoft Excel) available on the product website. These methods offer a ...

Page 24

Si4330-B1 fb[4:0] Value The chip will automatically shift the frequency of the Synthesizer down by 937.5 ...

Page 25

Easy Frequency Programming for FHSS While Registers 73h–77h may be used to program the carrier frequency of the Si4330 often easier to think in terms of “channels” or “channel numbers” rather than an absolute frequency value in ...

Page 26

Si4330-B1 3.5.4. Frequency Offset Adjustment When the AFC is disabled the frequency offset can be adjusted manually by fo[9:0] in registers 73h and 74h not possible to have both AFC and offset as internally they share the same ...

Page 27

When AFC is enabled, the preamble length needs to be long enough to settle the AFC. In general, one byte of preamble is sufficient to settle the AFC. Disabling the AFC allows the preamble to be shortened from 40 bits ...

Page 28

Si4330-B1 4. Modulation Options 4.1. FIFO Mode In FIFO mode, the receive data is stored in integrated FIFO register memory. The FIFOs are accessed via "Register 7Fh. FIFO Access," and are most efficiently accessed with burst read/write operation as discussed ...

Page 29

Internal Functional Blocks This section provides an overview some of the key blocks of the internal radio architecture. 5.1. RX LNA The input frequency range for the LNA is between 240–960 MHz. The LNA provides gain with a noise ...

Page 30

Si4330-B1 measurements for clear channel assessment (CCA), and carrier sense (CS) functionality. Frequency mistuning caused by crystal inaccuracies can be compensated by enabling the digital automatic frequency control (AFC) in receive mode. A comprehensive programmable packet handler including key features ...

Page 31

Crystal Oscillator The Si4330 includes an integrated 30 MHz crystal oscillator with a fast start-up time of less than 600 µs when a suitable parallel resonant crystal is used. The design is differential with the required crystal load capacitance ...

Page 32

Si4330-B1 6. Data Handling and Packet Handler The internal modem is designed to operate with a packet including a 10101... preamble structure. To configure the modem to operate with packet formats without a preamble or other legacy packet structures contact ...

Page 33

Packet Configuration When using the FIFO, automatic packet handling may be enabled for the RX mode. "Register 30h. Data Access Control" through “Register 39h. Synchronization Word 0,” on page 99 and “Register 3Fh. Check Header 3,” on page 100 ...

Page 34

Si4330-B1 Transmission: Register H eader(s) Data Register L ength Data Data FIFO Figure 13. Multiple Packets in RX Packet Handler Initial state FIFO Addr. RX FIFO Addr. Write 0 0 Pointer H L Data 63 63 ...

Page 35

Add R/W Function/Description D7 30 R/W Data Access Control enpacrx 31 R EzMAC status Reserved 32 R/W Header Control 1 bcen[3] 33 R/W Header Control 2 skipsyn 34 R/W Preamble Length prealen[7] 35 R/W Preamble Detection Control preath[4] 36 R/W ...

Page 36

Si4330-B1 6.4. Data Whitening, Manchester Encoding, and CRC Data whitening can be used to avoid extended sequences the transmitted data stream to achieve a more uniform spectrum. When enabled, the payload data bits are XORed ...

Page 37

Preamble Length The preamble detection threshold determines the number of valid preamble bits the radio must receive to qualify a valid preamble. The preamble threshold should be adjusted depending on the nature of the application. The required preamble length ...

Page 38

Si4330-B1 initiated. The timeout period after preamble detections is defined as the value programmed into the sync word length plus four additional bits. 6.9. Receive Header Check The header check is designed to support 1–4 bytes and broadcast headers. The ...

Page 39

RX Modem Configuration A Microsoft Excel (WDS) parameter calculator or Wireless Development Suite (WDS) calculator is provided to determine the proper settings for the modem. The calculator can be found on www.silabs.com or on the CD provided with the ...

Page 40

Si4330-B1 8. Auxiliary Functions 8.1. Smart Reset The Si4330 contains an enhanced integrated SMART RESET or POR circuit. The POR circuit contains both a classic level threshold reset as well as a slope detector POR. This reset circuit was designed ...

Page 41

Microcontroller Clock The 30 MHz crystal oscillator frequency is divided down internally and may be output to the microcontroller through GPIO2. This feature is useful to lower BOM cost by using only one crystal in the system. The system ...

Page 42

Si4330-B1 8.3. General Purpose ADC An 8-bit SAR ADC is integrated for general purpose use, as well as for digitizing the on-chip temperature sensor reading. Registers 0Fh "ADC Configuration", 10h "Sensor Offset" and 4Fh "Amplifier Offset" can be used to ...

Page 43

Temperature Sensor An integrated on-chip analog temperature sensor is available. The temperature sensor will be automatically enabled when the temperature sensor is selected as the input of the ADC or when the analog temp voltage is selected on the ...

Page 44

Si4330-B1 Temperature Measurement with ADC8 300 250 200 150 100 50 0 -40 -20 Figure 20. Temperature Ranges using ADC8 Temperature [Celsius] Rev 1.0 Sensor Range 0 Sensor Range 1 Sensor Range 2 Sensor ...

Page 45

Low Battery Detector A low battery detector (LBD) with digital read-out is integrated into the chip. A digital threshold may be programmed into the lbdt[4:0] field in "Register 1Ah. Low Battery Detector Threshold." When the digitized battery voltage reaches ...

Page 46

Si4330-B1 8.6. Wake-Up Timer and 32 kHz Clock Source The chip contains an integrated wake-up timer which can be used to periodically wake the chip from SLEEP mode. The wake-up timer runs from the internal 32.768 kHz RC Oscillator. The ...

Page 47

WUT Period GPIOX =00001 nIRQ SPI Interrupt Read Chip State Sleep Ready 1.5 mA Current Consumption WUT Period GPIOX =00001 nIRQ SPI Interrupt Read Chip State Current Consumption Figure 21. WUT Interrupt and WUT Operation Interrupt Enable enwut =1 ( ...

Page 48

Si4330-B1 8.7. Low Duty Cycle Mode The Low Duty Cycle Mode is available to automatically wake-up the receiver to check if a valid signal is available. The basic operation of the low duty cycle mode is demonstrated in the figure ...

Page 49

GPIO Configuration Three general purpose IOs (GPIOs) are available. Numerous functions such as specific interrupts, Antenna Diversity Switch control, Microcontroller Output, etc. can be routed to the GPIO pins as shown in the tables below. When in Shutdown mode ...

Page 50

Si4330-B1 8.9. Antenna Diversity To mitigate the problem of frequency-selective fading due to multi-path propagation, some radio systems use a scheme known as antenna diversity. In this scheme, two antennas are used. Each time the radio enters RX mode the ...

Page 51

RSSI and Clear Channel Assessment Received signal strength indicator (RSSI estimate of the signal strength in the channel to which the receiver is tuned. The RSSI value can be read from an 8-bit register with 0.5 dB ...

Page 52

Si4330-B1 9. Reference Design Reference designs are available at schematics, BOM, and layout. RX matching component values for different frequency bands can be found in “AN427: EZRadioPRO Si433x and Si443x RX LNA Matching.” 52 www.silabs.com for many common applications which ...

Page 53

... AN462: Extended battery life using the EZRadioPRO and a DC-DC Buck Converter AN463: Support for Non-Standard Packet Structures and RAW Mode AN466: Si4030/31/32 Register Descriptions AN467: Si4330 Register Descriptions 11. Customer Support Technical support for the complete family of Silicon Labs wireless products is available by accessing the wireless section of the Silicon Labs' website at www ...

Page 54

Si4330-B1 12. Register Table and Descriptions Add R/W Function/Desc 01 R Device Version 02 R Device Status 03 R Interrupt Status Interrupt Status 2 05 R/W Interrupt Enable 1 06 R/W Interrupt Enable 2 07 R/W Operating ...

Page 55

Add R/W Function/Desc 28 R Antenna Diversity Register Antenna Diversity Register 2 2A R/W AFC Limiter 2B R AFC Correction Read 2C R/W OOK Counter Value 1 2D R/W OOK Counter Value 2 2E R/W Slicer Peak ...

Page 56

Si4330-B1 Table 17. Register Descriptions (Continued) Add R/W Function/Desc 75 R/W Frequency Band Select Reserved 76 R/W Nominal Carrier Frequency 1 77 R/W Nominal Carrier Frequency R/W Frequency Hopping Channel Select 7A R/W Frequency Hopping Step Size ...

Page 57

Pin Descriptions: Si4330 Pin Pin Name I/O 1 VDD_RF VDD +1.8 to +3.6 V supply voltage input to all analog +1.7 V regulators. The recommended — No Connect. 3 RXp I Differential RF ...

Page 58

Si4330-B1 14. Ordering Information Part Number* Si4330-B1-FM ISM EZRadioPRO Receiver *Note: Add an “(R)” at the end of the device part number to denote tape and reel option; 2500 quantity per reel. 58 Description Rev 1.0 Package Operating Type Temperature ...

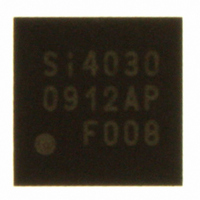

Page 59

Package Markings (Top Marks) 15.1. Si4330 Top Mark 15.2. Top Mark Explanation Mark Method: YAG Laser Line 1 Marking Part Number Line 2 Marking Die Revision TTTTT = Internal Code Line 3 Marking: YY= Year ...

Page 60

Si4330-B1 16. Package Outline: Si4330 Figure 25 illustrates the package details for the Si4330. Table 23 lists the values for the dimensions shown in the illustration. Figure 25. 20-Pin Quad Flat No-Lead (QFN) Symbol ...

Page 61

PCB Land Pattern: Si4330 Figure 26 illustrates the PCB land pattern details for the Si4330. Table 24 lists the values for the dimensions shown in the illustration. Figure 26. PCB Land Pattern Rev 1.0 Si4330-B1 61 ...

Page 62

Si4330-B1 Table 19. PCB Land Pattern Dimensions Symbol Notes: General 1. All dimensions shown are in millimeters (mm) unless otherwise noted. 2. This land pattern design is based on IPC-7351 guidelines. Note: Solder ...

Page 63

OCUMENT HANGE IST Revision 0.1 to Revision 0.2 Updated register descriptions Revision 0.2 to Revision 0.3 Added Max Shutdown and Standby Currents and adjusted typical values. Increased datarate to 256 kbps. Updated Table ...

Page 64

... Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized ap- plication, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages. Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc. Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders. ...