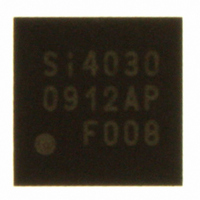

SI4030-A0-FM Silicon Laboratories Inc, SI4030-A0-FM Datasheet - Page 21

SI4030-A0-FM

Manufacturer Part Number

SI4030-A0-FM

Description

IC TX ISM 930MHZ 3.6V 20-QFN

Manufacturer

Silicon Laboratories Inc

Type

ISM Transmitterr

Specifications of SI4030-A0-FM

Package / Case

20-QFN

Frequency

240MHz ~ 930MHz

Modulation Or Protocol

FSK, GFSK, OOK

Data Rate - Maximum

128kbps

Power - Output

20dBm (100mW)

Current - Transmitting

28mA

Data Interface

PCB, Surface Mount

Antenna Connector

PCB, Surface Mount

Voltage - Supply

1.8 V ~ 3.6 V

Operating Temperature

-40°C ~ 85°C

Operating Frequency

240 MHz to 960 MHz

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Supply Current

100 nA

Supply Voltage (max)

3.6 V

Supply Voltage (min)

1.8 V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Applications

-

Memory Size

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Other names

336-1624-5

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

SI4030-A0-FM

Manufacturer:

SILICON

Quantity:

120

Part Number:

SI4030-A0-FM

Manufacturer:

SILICONLABS/èٹ¯ç§‘

Quantity:

20 000

3.3. Interrupts

The Si4330 is capable of generating an interrupt signal when certain events occur. The chip notifies the

microcontroller that an interrupt event has occurred by setting the nIRQ output pin LOW = 0. This interrupt signal

will be generated when any one (or more) of the interrupt events (corresponding to the Interrupt Status bits) shown

below occur. The nIRQ pin will remain low until the microcontroller reads the Interrupt Status Register(s) (Registers

03h–04h) containing the active Interrupt Status bit. The nIRQ output signal will then be reset until the next change

in status is detected. The interrupts must be enabled by the corresponding enable bit in the Interrupt Enable

Registers (Registers 05h–06h). All enabled interrupt bits will be cleared when the microcontroller reads the

interrupt status register. If the interrupt is not enabled when the event occurs it will not trigger the nIRQ pin, but the

status may still be read at anytime in the Interrupt Status registers.

Add R/W Function/Descript

For a complete descriptions of each interrupt, see “AN467: Si4330 Register Descriptions.”

03

04

05 R/W

06 R/W

R

R

Interrupt Enable 1

Interrupt Enable 2

Interrupt Status 1

Interrupt Status 2

ion

enswdet enpreaval enpreainval

enfferr

iswdet

ifferr

D7

Reserved Reserved

Reserved Reserved enrxffafull enext Reserved enpkvalid encrcerror

ipreaval

D6

ipreainval

D5

Rev 1.0

irxffafull

enrssi

irssi

D4

enwut

iwut

iext Reserved ipkvalid

D3

enlbd

ilbd

D2

enchiprdy

ichiprdy

D1

Si4330-B1

icrcerror

enpor

ipor

D0

POR Def.

00h

01h

—

—

21