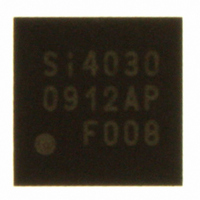

SI4030-A0-FM Silicon Laboratories Inc, SI4030-A0-FM Datasheet - Page 28

SI4030-A0-FM

Manufacturer Part Number

SI4030-A0-FM

Description

IC TX ISM 930MHZ 3.6V 20-QFN

Manufacturer

Silicon Laboratories Inc

Type

ISM Transmitterr

Specifications of SI4030-A0-FM

Package / Case

20-QFN

Frequency

240MHz ~ 930MHz

Modulation Or Protocol

FSK, GFSK, OOK

Data Rate - Maximum

128kbps

Power - Output

20dBm (100mW)

Current - Transmitting

28mA

Data Interface

PCB, Surface Mount

Antenna Connector

PCB, Surface Mount

Voltage - Supply

1.8 V ~ 3.6 V

Operating Temperature

-40°C ~ 85°C

Operating Frequency

240 MHz to 960 MHz

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Supply Current

100 nA

Supply Voltage (max)

3.6 V

Supply Voltage (min)

1.8 V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Applications

-

Memory Size

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Other names

336-1624-5

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

SI4030-A0-FM

Manufacturer:

SILICON

Quantity:

120

Part Number:

SI4030-A0-FM

Manufacturer:

SILICONLABS/èٹ¯ç§‘

Quantity:

20 000

Si4330-B1

4. Modulation Options

4.1. FIFO Mode

In FIFO mode, the receive data is stored in integrated FIFO register memory. The FIFOs are accessed via

"Register 7Fh. FIFO Access," and are most efficiently accessed with burst read/write operation as discussed in

"3.1. Serial Peripheral Interface (SPI)" on page 16.

In RX mode, only the bytes of the received packet structure that are considered to be "data bytes" are stored in

FIFO memory. Which bytes of the received packet are considered "data bytes" is determined by the Automatic

Packet Handler (if enabled), in conjunction with the Packet Handler Registers (see Table 12 on page 35). If the

Automatic Packet Handler is disabled, all bytes following the Sync word are considered data bytes and are stored

in FIFO memory. Thus, even if Automatic Packet Handling operation is not desired, the preamble detection

threshold and Sync word still need to be programmed so that the RX Modem knows when to start filling data into

the FIFO. When the FIFO is being used in RX mode, all of the received data may still be observed directly (in real-

time) by properly programming a GPIO pin as the RXDATA output pin; this can be quite useful during application

development.

When in FIFO mode, the chip will automatically exit the RX State when either the ipksent or ipkvalid interrupt

occurs. The chip will return to any of the other states based on the settings in "Register 07h. Operating Mode and

Function Control 1."

In RX mode, the rxon bit will be cleared if ipkvalid occurs and the rxmpk bit (RX Multi-Packet bit, SPI Register 08h

bit [4]) is not set. When the rxmpk bit is set, the part will not exit the RX state after successfully receiving a packet,

but will remain in RX mode. The microcontroller will need to decide on the appropriate subsequent action,

depending upon information such as an interrupt generated by CRC, packet valid, or preamble detect.

28

Rev 1.0