AD8396ACPZ-RL Analog Devices Inc, AD8396ACPZ-RL Datasheet - Page 9

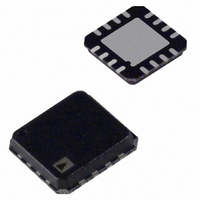

AD8396ACPZ-RL

Manufacturer Part Number

AD8396ACPZ-RL

Description

ADSL+2 DSL Line Driver For CO

Manufacturer

Analog Devices Inc

Type

Line Driver, Transmitterr

Datasheet

1.AD8396ACPZ-R7.pdf

(12 pages)

Specifications of AD8396ACPZ-RL

Number Of Drivers/receivers

2/0

Voltage - Supply

6 V ~ 24 V

Mounting Type

Surface Mount

Package / Case

16-LFCSP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Protocol

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

APPLICATIONS INFORMATION

SUPPLIES, GROUNDING, AND LAYOUT

The AD8396 can be powered from either single or dual supplies,

with the total supply voltage ranging from 12 V to 24 V. For

optimum performance, use well-regulated low ripple supplies.

As with all high speed amplifiers, pay close attention to supply

decoupling, grounding, and overall board layout. Provide low

frequency supply decoupling with 10 μF tantalum capacitors

from each supply to ground. In addition, decouple all supply

pins with 0.1 μF quality ceramic chip capacitors placed as close

as possible to the driver. Use an internal low impedance ground

plane to provide a common ground point for all driver and

decoupling capacitor ground requirements. Whenever possible,

use separate ground planes for analog and digital circuitry.

Follow high speed layout techniques to minimize parasitic

capacitance.

Keep input and output traces as short as possible and as far

apart from each other as practical to minimize crosstalk. Keep

all differential signal traces as symmetrical as possible.

POWER MANAGEMENT

A digitally programmable logic pin switches each port of the

AD8396 between active bias and shutdown states. The PD_A

pin controls Port A and the PD_B pin controls Port B. These

pins can be controlled directly with either 3.3 V or 5 V CMOS

logic with the DGND pins as a reference. If left unconnected,

the PD pins float high, placing the amplifier in the shutdown

state. See the Specifications section for the quiescent current for

each of the available bias states.

TYPICAL ADSL/ADSL2+ APPLICATION

In a typical ADSL/ADSL2+ application, a differential line driver

takes the signal from the analog front end (AFE) and drives it

onto the twisted pair telephone line. Referring to the typical

circuit representation in Figure 14, the differential input appears

at V

transformer coupled to the telephone line at TIP and RING.

The common-mode operating point, generally midway between

the supplies, is set internally and is available at VCOM.

V

V

VCOM

IN+

IN–

0.1µF

IN+

and V

Figure 14. Typical ADSL/ADSL2+ Application Circuit

IN−

from the AFE, while the differential output is

4kΩ

4kΩ

VCC

VEE

+

–

–

+

R

R

m

m

1:N

TIP

RING

R

OUT

Rev. C | Page 9 of 12

MULTITONE POWER RATIO (MTPR)

The DMT signal used in ADSL/ADSL2+ systems carries data in

discrete tones or bins, which appear in the frequency domain in

evenly spaced 4.3125 kHz intervals. In applications using this type

of waveform, MTPR is a commonly used measure of linearity.

Generally, designers are concerned with two types of MTPR:

in-band and out-of-band. In-band MTPR is defined as the

measured difference from the peak of one tone that is loaded

with data to the peak of an adjacent tone that is intentionally

left empty. Out-of-band MTPR is more loosely defined as the

spurious emissions that occur in the receive band located between

25.875 kHz and the first downstream tone at 138 kHz. Figure 15

and Figure 16 show the AD8396 in-band MTPR for a 5.5 crest

factor waveform for empty bins in the ADSL and extended

ADSL2+ bandwidths.

–100

–100

–10

–20

–30

–40

–50

–60

–70

–80

–90

–10

–20

–30

–40

–50

–60

–70

–80

–90

642.131

1.9618

0

0

Figure 15. In-Band MTPR at 646.875 kHz

Figure 16. In-Band MTPR at 1.9665 MHz

644.503

1.9641

FREQUENCY (MHz)

FREQUENCY (kHz)

–73dBc

–68dBc

646.875

1.9665

649.247

1.9689

AD8396

651.619

1.9712