KSZ8851-16MLL TR Micrel Inc, KSZ8851-16MLL TR Datasheet - Page 21

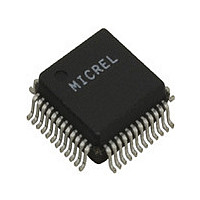

KSZ8851-16MLL TR

Manufacturer Part Number

KSZ8851-16MLL TR

Description

Single Ethernet Port + Generic (16-bit) Bus Interface( )

Manufacturer

Micrel Inc

Datasheet

1.KSZ8851-16MLL_TR.pdf

(79 pages)

Specifications of KSZ8851-16MLL TR

Operating Supply Voltage (typ)

3.3V

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

48

Lead Free Status / RoHS Status

Compliant

Micrel, Inc.

KSZ8851-16MLL/MLLI

test enable bit, P1SCLMD [12], is set to ‘1’ to start the test on this pair.

When bit P1SCLMD[12] returns to ‘0’, the test is complete. The test result is returned in bits P1SCLMD[14:13] and the

distance is returned in bits P1SCLMD[8:0]. The cable diagnostic test results are as follows:

00 = Valid test, normal condition

01 = Valid test, open circuit in cable

10 = Valid test, short circuit in cable

®

11 = Invalid test, LinkMD

failed

If P1SCLMD[14:13]=11, this indicates an invalid test, and occurs when the KSZ8851-16MLL is unable to shut down the

link partner. In this instance, the test is not run, as it is not possible for the KSZ8851-16MLL to determine if the detected

signal is a reflection of the signal generated or a signal from another source.

Cable distance can be approximated by the following formula:

P1SCLMD[8:0] x 0.4m for port 1 cable distance

This constant may be calibrated for different cabling conditions, including cables with a velocity of propagation that varies

significantly from the norm.

Media Access Control (MAC) Operation

The KSZ8851-16MLL strictly abides by IEEE 802.3 standards to maximize compatibility.

Inter Packet Gap (IPG)

If a frame is successfully transmitted, then the minimum 96-bit time for IPG is measured between two consecutive

packets. If the current packet is experiencing collisions, the minimum 96-bit time for IPG is measured from carrier sense

(CRS) to the next transmit packet.

Back-Off Algorithm

The KSZ8851-16MLL implements the IEEE standard 802.3 binary exponential back-off algorithm in half-duplex mode.

After 16 collisions, the packet is dropped.

Late Collision

If a transmit packet experiences collisions after 512 bit times of the transmission, the packet is dropped.

Flow Control

The KSZ8851-16MLL supports standard 802.3x flow control frames on both transmit and receive sides.

On the receive side, if the KSZ8851-16MLL receives a pause control frame, the KSZ8851-16MLL will not transmit the next

normal frame until the timer, specified in the pause control frame, expires. If another pause frame is received before the

current timer expires, the timer will be updated with the new value in the second pause frame. During this period (while it

is flow controlled), only flow control packets from the KSZ8851-16MLL are transmitted.

On the transmit side, the KSZ8851-16MLL has intelligent and efficient ways to determine when to invoke flow control. The

flow control is based on availability of the system resources.

There are three programmable low watermark register FCLWR (0xB0), high watermark register FCHWR (0xB2) and

overrun watermark register FCOWR (0xB4) for flow control in RXQ FIFO. The KSZ8851-16MLL will send PAUSE frame

when the RXQ buffer hit the high watermark level (default 3.072KByte available) and stop PAUSE frame when the RXQ

buffer hit the low watermark level (default 5.12KByte available). The KSZ8851-16MLL will drop packet when the RXQ

buffer hit the overrun watermark level (default 256-Byte available).

The KSZ8851-16MLL issues a flow control frame (Xoff, or transmitter off), containing the maximum pause time defined in

IEEE standard 802.3x. Once the resource is freed up, the KSZ8851-16MLL sends out the another flow control frame

(Xon, or transmitter on) with zero pause time to turn off the flow control (turn on transmission to the port). A hysteresis

feature is provided to prevent the flow control mechanism from being constantly activated and deactivated.

August 2009

21

M9999-083109-2.0